1 20 2 20 3 10 4 20 5 20 6 20 7 20 8 20 150 Note - Ing. H. Heuermann

1 20 2 20 3 10 4 20 5 20 6 20 7 20 8 20 150 Note - Ing. H. Heuermann

1 20 2 20 3 10 4 20 5 20 6 20 7 20 8 20 150 Note - Ing. H. Heuermann

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

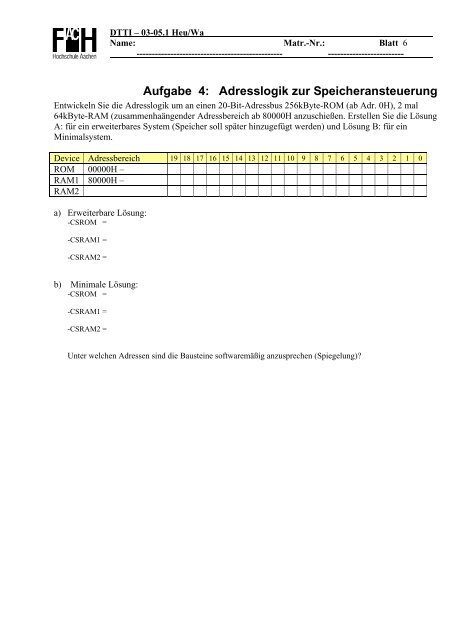

DTTI – 03-05.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 6<br />

------------------------------------------------ -------------------------<br />

Aufgabe 4: Adresslogik zur Speicheransteuerung<br />

Entwickeln Sie die Adresslogik um an einen <strong>20</strong>-Bit-Adressbus 256kByte-ROM (ab Adr. 0H), 2 mal<br />

64kByte-RAM (zusammenhaängender Adressbereich ab 80000H anzuschießen. Erstellen Sie die Lösung<br />

A: für ein erweiterbares System (Speicher soll später hinzugefügt werden) und Lösung B: für ein<br />

Minimalsystem.<br />

Device Adressbereich 19 18 17 16 15 14 13 12 11 <strong>10</strong> 9 8 7 6 5 4 3 2 1 0<br />

ROM 00000H –<br />

RAM1 80000H –<br />

RAM2<br />

a) Erweiterbare Lösung:<br />

-CSROM =<br />

-CSRAM1 =<br />

-CSRAM2 =<br />

b) Minimale Lösung:<br />

-CSROM =<br />

-CSRAM1 =<br />

-CSRAM2 =<br />

Unter welchen Adressen sind die Bausteine softwaremäßig anzusprechen (Spiegelung)?