Testexperimente zur akustischen Navigation in Eis und Wasser für ...

Testexperimente zur akustischen Navigation in Eis und Wasser für ...

Testexperimente zur akustischen Navigation in Eis und Wasser für ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

PCIe<br />

Signalteiler<br />

PA 4<br />

PA 3<br />

PA 2 PA 1<br />

3 Die <strong>Eis</strong>schmelzsonde IceMole 19<br />

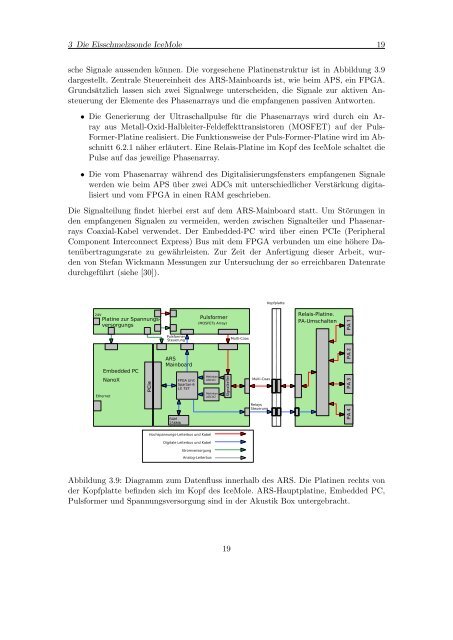

sche Signale aussenden können. Die vorgesehene Plat<strong>in</strong>enstruktur ist <strong>in</strong> Abbildung 3.9<br />

dargestellt. Zentrale Steuere<strong>in</strong>heit des ARS-Ma<strong>in</strong>boards ist, wie beim APS, e<strong>in</strong> FPGA.<br />

Gr<strong>und</strong>sätzlich lassen sich zwei Signalwege unterscheiden, die Signale <strong>zur</strong> aktiven Ansteuerung<br />

der Elemente des Phasenarrays <strong>und</strong> die empfangenen passiven Antworten.<br />

• Die Generierung der Ultraschallpulse <strong>für</strong> die Phasenarrays wird durch e<strong>in</strong> Array<br />

aus Metall-Oxid-Halbleiter-Feldeffekttransistoren (MOSFET) auf der Puls-<br />

Former-Plat<strong>in</strong>e realisiert. Die Funktionsweise der Puls-Former-Plat<strong>in</strong>e wird im Abschnitt<br />

6.2.1 näher erläutert. E<strong>in</strong>e Relais-Plat<strong>in</strong>e im Kopf des IceMole schaltet die<br />

Pulse auf das jeweilige Phasenarray.<br />

• Die vom Phasenarray während des Digitalisierungsfensters empfangenen Signale<br />

werden wie beim APS über zwei ADCs mit unterschiedlicher Verstärkung digitalisiert<br />

<strong>und</strong> vom FPGA <strong>in</strong> e<strong>in</strong>en RAM geschrieben.<br />

Die Signalteilung f<strong>in</strong>det hierbei erst auf dem ARS-Ma<strong>in</strong>board statt. Um Störungen <strong>in</strong><br />

den empfangenen Signalen zu vermeiden, werden zwischen Signalteiler <strong>und</strong> Phasenarrays<br />

Coaxial-Kabel verwendet. Der Embedded-PC wird über e<strong>in</strong>en PCIe (Peripheral<br />

Component Interconnect Express) Bus mit dem FPGA verb<strong>und</strong>en um e<strong>in</strong>e höhere Datenübertragungsrate<br />

zu gewährleisten. Zur Zeit der Anfertigung dieser Arbeit, wurden<br />

von Stefan Wickmann Messungen <strong>zur</strong> Untersuchung der so erreichbaren Datenrate<br />

durchgeführt (siehe [30]).<br />

Architektur Feldtest des ARS-Systems 3. <strong>für</strong><br />

Kopfplatte<br />

24V<br />

Plat<strong>in</strong>e <strong>zur</strong> Spannungsversorgungs<br />

Pulsformer<br />

(MOSFETs Array)<br />

Relais-Plat<strong>in</strong>e.<br />

PA-Umschalten<br />

Pulsformer<br />

Steuerung<br />

Multi-Coax<br />

Embedded PC<br />

NanoX<br />

Ethernet<br />

ARS<br />

Ma<strong>in</strong>board<br />

FPGA Unit<br />

Spartan-6<br />

LX 75T<br />

Mehrkan.<br />

ADC#1<br />

Mehrkan.<br />

ADC#2<br />

Multi-Coax<br />

Relays<br />

Steuerung<br />

RAM<br />

256Mb<br />

Hochspannungs-Leiterbus <strong>und</strong> Kabel<br />

Digitale Leiterbus <strong>und</strong> Kabel<br />

Stromversorgung<br />

Analog-Leiterbus<br />

Abbildung 3.9: Diagramm zum Datenfluss <strong>in</strong>nerhalb des ARS. Die Plat<strong>in</strong>en rechts von<br />

der Kopfplatte bef<strong>in</strong>den sich im Kopf des IceMole. ARS-Hauptplat<strong>in</strong>e, Embedded PC,<br />

Pulsformer <strong>und</strong> Spannungsversorgung s<strong>in</strong>d <strong>in</strong> der Akustik Box untergebracht.<br />

19