Visualisierung von Parametern komplexer Schnittstellen ... - ihmor.de

Visualisierung von Parametern komplexer Schnittstellen ... - ihmor.de

Visualisierung von Parametern komplexer Schnittstellen ... - ihmor.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Category (ipq:M..256):<br />

Die Board-Kategorie ordnet <strong>de</strong>m Board einen bestimmten Typ zu. Hierbei bietet das IFS<br />

Format mittels <strong>de</strong>r Technik <strong>de</strong>r Enumerations bis jetzt zwei Typen zur Auswahl an. Eine<br />

spätere Erweiterung <strong>de</strong>s Schemas ist möglich. Die Beschränkung auf die Typen Altera UP1<br />

und Spy<strong>de</strong>r Virtex XCV300 begrün<strong>de</strong>t sich darin, dass bisher ausschließlich diese bei<strong>de</strong>n<br />

FPGA-Board Typen verwen<strong>de</strong>t wur<strong>de</strong>n.<br />

Die Versionsangaben aus Version sind selbstverständlich auch in Board vorhan<strong>de</strong>n. Ebenso<br />

wie das System besitzt ein Board die Parametergruppen InterfaceMapList und MediumList.<br />

Die Funktion dieser Parameter wird später an passen<strong>de</strong>r Stelle näher erläutert. Die<br />

nachfolgen<strong>de</strong> Hierarchieebene ist die Menge an Chips, die auf einem Board vorhan<strong>de</strong>n sind<br />

und in <strong>de</strong>r ChipList zusammengefasst wer<strong>de</strong>n. Das Board ist die erste Komponente, die<br />

<strong>Schnittstellen</strong> aufweist. Diese wer<strong>de</strong>n in <strong>de</strong>r InterfaceList verwaltet. Eine genaue<br />

Beschreibung <strong>de</strong>r <strong>Schnittstellen</strong> wird in 4.3 später erbracht.<br />

Die exakte XML Notation <strong>de</strong>s Board-Schemas befin<strong>de</strong>t sich im Anhang unter 8.1.2.3.<br />

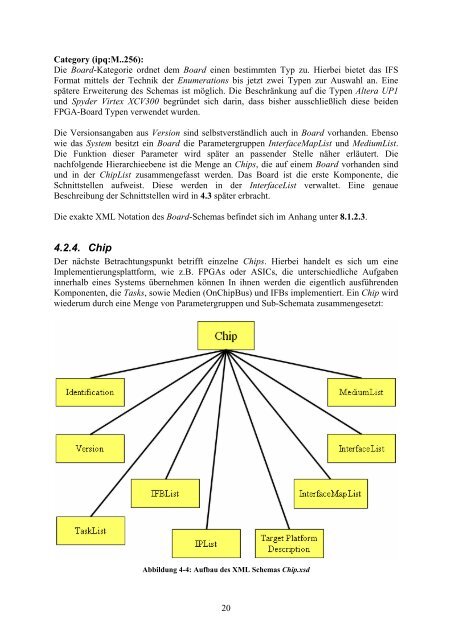

4.2.4. Chip<br />

Der nächste Betrachtungspunkt betrifft einzelne Chips. Hierbei han<strong>de</strong>lt es sich um eine<br />

Implementierungsplattform, wie z.B. FPGAs o<strong>de</strong>r ASICs, die unterschiedliche Aufgaben<br />

innerhalb eines Systems übernehmen können In ihnen wer<strong>de</strong>n die eigentlich ausführen<strong>de</strong>n<br />

Komponenten, die Tasks, sowie Medien (OnChipBus) und IFBs implementiert. Ein Chip wird<br />

wie<strong>de</strong>rum durch eine Menge <strong>von</strong> Parametergruppen und Sub-Schemata zusammengesetzt:<br />

Abbildung 4-4: Aufbau <strong>de</strong>s XML Schemas Chip.xsd<br />

20