Visualisierung von Parametern komplexer Schnittstellen ... - ihmor.de

Visualisierung von Parametern komplexer Schnittstellen ... - ihmor.de

Visualisierung von Parametern komplexer Schnittstellen ... - ihmor.de

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

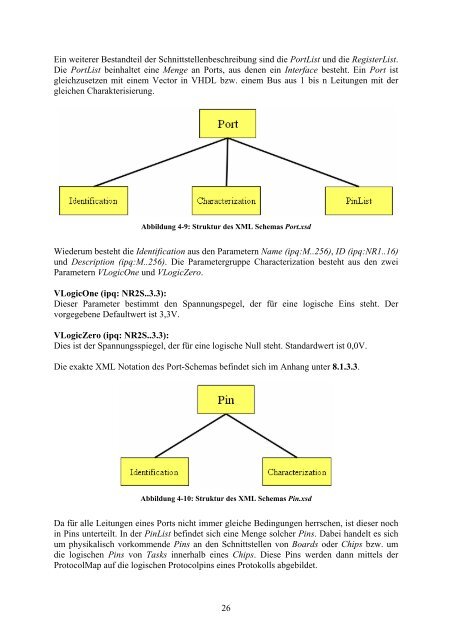

Ein weiterer Bestandteil <strong>de</strong>r <strong>Schnittstellen</strong>beschreibung sind die PortList und die RegisterList.<br />

Die PortList beinhaltet eine Menge an Ports, aus <strong>de</strong>nen ein Interface besteht. Ein Port ist<br />

gleichzusetzen mit einem Vector in VHDL bzw. einem Bus aus 1 bis n Leitungen mit <strong>de</strong>r<br />

gleichen Charakterisierung.<br />

Abbildung 4-9: Struktur <strong>de</strong>s XML Schemas Port.xsd<br />

Wie<strong>de</strong>rum besteht die I<strong>de</strong>ntification aus <strong>de</strong>n <strong>Parametern</strong> Name (ipq:M..256), ID (ipq:NR1..16)<br />

und Description (ipq:M..256). Die Parametergruppe Characterization besteht aus <strong>de</strong>n zwei<br />

<strong>Parametern</strong> VLogicOne und VLogicZero.<br />

VLogicOne (ipq: NR2S..3.3):<br />

Dieser Parameter bestimmt <strong>de</strong>n Spannungspegel, <strong>de</strong>r für eine logische Eins steht. Der<br />

vorgegebene Defaultwert ist 3,3V.<br />

VLogicZero (ipq: NR2S..3.3):<br />

Dies ist <strong>de</strong>r Spannungsspiegel, <strong>de</strong>r für eine logische Null steht. Standardwert ist 0,0V.<br />

Die exakte XML Notation <strong>de</strong>s Port-Schemas befin<strong>de</strong>t sich im Anhang unter 8.1.3.3.<br />

Abbildung 4-10: Struktur <strong>de</strong>s XML Schemas Pin.xsd<br />

Da für alle Leitungen eines Ports nicht immer gleiche Bedingungen herrschen, ist dieser noch<br />

in Pins unterteilt. In <strong>de</strong>r PinList befin<strong>de</strong>t sich eine Menge solcher Pins. Dabei han<strong>de</strong>lt es sich<br />

um physikalisch vorkommen<strong>de</strong> Pins an <strong>de</strong>n <strong>Schnittstellen</strong> <strong>von</strong> Boards o<strong>de</strong>r Chips bzw. um<br />

die logischen Pins <strong>von</strong> Tasks innerhalb eines Chips. Diese Pins wer<strong>de</strong>n dann mittels <strong>de</strong>r<br />

ProtocolMap auf die logischen Protocolpins eines Protokolls abgebil<strong>de</strong>t.<br />

26