Elektronik für Physiker - Physik-Institut

Elektronik für Physiker - Physik-Institut

Elektronik für Physiker - Physik-Institut

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

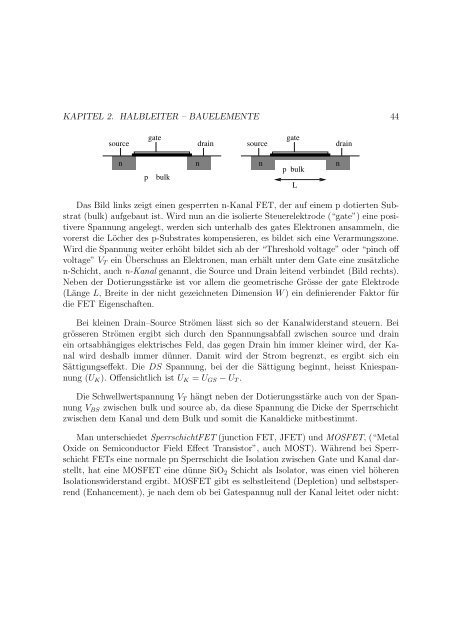

KAPITEL 2. HALBLEITER – BAUELEMENTE 44<br />

gate<br />

source drain<br />

n<br />

p<br />

bulk<br />

n<br />

gate<br />

source drain<br />

n n<br />

p bulk<br />

Das Bild links zeigt einen gesperrten n-Kanal FET, der auf einem p dotierten Substrat<br />

(bulk) aufgebaut ist. Wird nun an die isolierte Steuerelektrode (“gate”) eine positivere<br />

Spannung angelegt, werden sich unterhalb des gates Elektronen ansammeln, die<br />

vorerst die Löcher des p-Substrates kompensieren, es bildet sich eine Verarmungszone.<br />

Wird die Spannung weiter erhöht bildet sich ab der “Threshold voltage” oder “pinch off<br />

voltage” VT ein Überschuss an Elektronen, man erhält unter dem Gate eine zusätzliche<br />

n-Schicht, auch n-Kanal genannt, die Source und Drain leitend verbindet (Bild rechts).<br />

Neben der Dotierungsstärke ist vor allem die geometrische Grösse der gate Elektrode<br />

(Länge L, Breite in der nicht gezeichneten Dimension W ) ein definierender Faktor <strong>für</strong><br />

die FET Eigenschaften.<br />

Bei kleinen Drain–Source Strömen lässt sich so der Kanalwiderstand steuern. Bei<br />

grösseren Strömen ergibt sich durch den Spannungsabfall zwischen source und drain<br />

ein ortsabhängiges elektrisches Feld, das gegen Drain hin immer kleiner wird, der Kanal<br />

wird deshalb immer dünner. Damit wird der Strom begrenzt, es ergibt sich ein<br />

Sättigungseffekt. Die DS Spannung, bei der die Sättigung beginnt, heisst Kniespannung<br />

(UK). Offensichtlich ist UK = UGS − UT .<br />

Die Schwellwertspannung VT hängt neben der Dotierungsstärke auch von der Spannung<br />

VBS zwischen bulk und source ab, da diese Spannung die Dicke der Sperrschicht<br />

zwischen dem Kanal und dem Bulk und somit die Kanaldicke mitbestimmt.<br />

Man unterschiedet SperrschichtFET (junction FET, JFET) und MOSFET, (“Metal<br />

Oxide on Semiconductor Field Effect Transistor”, auch MOST). Während bei Sperrschicht<br />

FETs eine normale pn Sperrschicht die Isolation zwischen Gate und Kanal darstellt,<br />

hat eine MOSFET eine dünne SiO2 Schicht als Isolator, was einen viel höheren<br />

Isolationswiderstand ergibt. MOSFET gibt es selbstleitend (Depletion) und selbstsperrend<br />

(Enhancement), je nach dem ob bei Gatespannug null der Kanal leitet oder nicht:<br />

L