Switched-Capacitor Circuits - University of Toronto

Switched-Capacitor Circuits - University of Toronto

Switched-Capacitor Circuits - University of Toronto

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

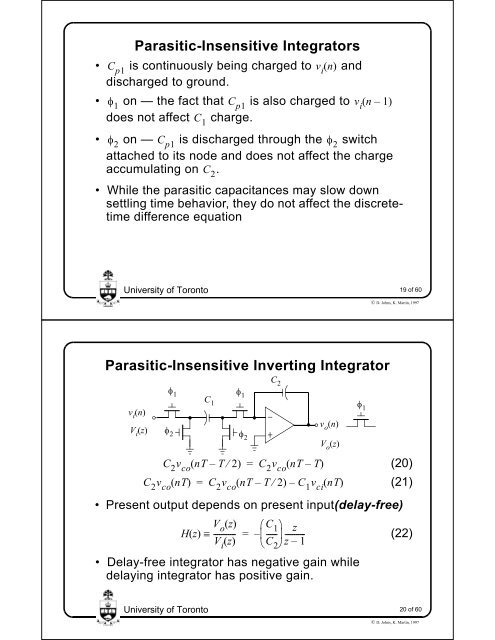

Parasitic-Insensitive Integrators<br />

• Cp1 is continuously being charged to vi( n)<br />

and<br />

discharged to ground.<br />

• 1 on — the fact that Cp1 is also charged to vi( n – 1)<br />

does not affect charge.<br />

C 1<br />

• 2 on — Cp1 is discharged through the 2 switch<br />

attached to its node and does not affect the charge<br />

accumulating on .<br />

C 2<br />

• While the parasitic capacitances may slow down<br />

settling time behavior, they do not affect the discretetime<br />

difference equation<br />

<strong>University</strong> <strong>of</strong> <strong>Toronto</strong><br />

Parasitic-Insensitive Inverting Integrator<br />

vi( n)<br />

Vi() z<br />

1<br />

<strong>University</strong> <strong>of</strong> <strong>Toronto</strong><br />

C 1<br />

1<br />

2 2<br />

19 <strong>of</strong> 60<br />

© D. Johns, K. Martin, 1997<br />

• Present output depends on present input(delay-free)<br />

C 2<br />

vo( n)<br />

Vo() z<br />

C2vco( nT – T 2)<br />

= C2vco( nT – T)<br />

C2vco( nT)<br />

= C2vco( nT – T 2)<br />

– C1vci( nT)<br />

Hz ()<br />

• Delay-free integrator has negative gain while<br />

delaying integrator has positive gain.<br />

Vo z () C1 z<br />

----------- =<br />

– ----- ----------<br />

Vi() z C2z– 1<br />

1<br />

(20)<br />

(21)<br />

(22)<br />

20 <strong>of</strong> 60<br />

© D. Johns, K. Martin, 1997