DRAM Technology

DRAM Technology

DRAM Technology

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

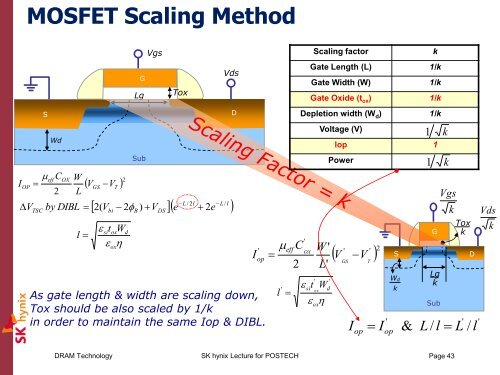

MOSFET Scaling Method<br />

S<br />

Wd<br />

eff COX<br />

W<br />

IOP GS <br />

2 L<br />

<br />

TSC<br />

2 V V<br />

V by DIBL <br />

l <br />

T<br />

G<br />

Lg<br />

Sub<br />

Vgs<br />

Tox<br />

Vds<br />

L<br />

/ 2l<br />

L<br />

/ l<br />

2( V 2 ) V<br />

e 2e<br />

<br />

bi<br />

t<br />

<br />

si oxWd<br />

ox<br />

<br />

B<br />

As gate length & width are scaling down,<br />

Tox should be also scaled by 1/k<br />

in order to maintain the same Iop & DIBL.<br />

DS<br />

D<br />

I<br />

'<br />

op<br />

<br />

l<br />

eff<br />

' <br />

C<br />

2<br />

Scaling factor k<br />

Gate Length (L) 1/k<br />

Gate Width (W) 1/k<br />

Gate Oxide (t ox) 1/k<br />

Depletion width (W d) 1/k<br />

'<br />

Voltage (V)<br />

W '<br />

L'<br />

Iop 1<br />

Power<br />

2 ' '<br />

V <br />

OX V<br />

GS T<br />

t<br />

' '<br />

si Wd<br />

<br />

ox<br />

ox<br />

<br />

'<br />

Iop Iop<br />

G<br />

S D<br />

Wd<br />

k<br />

1<br />

1<br />

Lg<br />

k<br />

Sub<br />

k<br />

k<br />

Vgs<br />

k<br />

Tox<br />

k<br />

' '<br />

& L / l L / l<br />

<strong>DRAM</strong> <strong>Technology</strong> SK hynix Lecture for POSTECH<br />

Page 43<br />

Vds<br />

k