hardware implementation of data compression ... - INFN Bologna

hardware implementation of data compression ... - INFN Bologna

hardware implementation of data compression ... - INFN Bologna

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

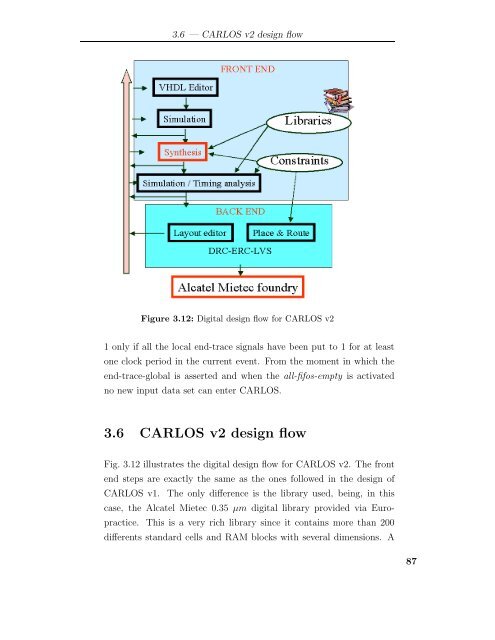

3.6 — CARLOS v2 design flow<br />

Figure 3.12: Digital design flow for CARLOS v2<br />

1 only if all the local end-trace signals have been put to 1 for at least<br />

one clock period in the current event. From the moment in which the<br />

end-trace-global is asserted and when the all-fifos-empty is activated<br />

no new input <strong>data</strong> set can enter CARLOS.<br />

3.6 CARLOS v2 design flow<br />

Fig. 3.12 illustrates the digital design flow for CARLOS v2. The front<br />

end steps are exactly the same as the ones followed in the design <strong>of</strong><br />

CARLOS v1. The only difference is the library used, being, in this<br />

case, the Alcatel Mietec 0.35 µm digital library provided via Europractice.<br />

This is a very rich library since it contains more than 200<br />

differents standard cells and RAM blocks with several dimensions. A<br />

87