24-Bit, 192-kHz Sampling, Advanced Segment, Audio Stereo DAC ...

24-Bit, 192-kHz Sampling, Advanced Segment, Audio Stereo DAC ...

24-Bit, 192-kHz Sampling, Advanced Segment, Audio Stereo DAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

www.ti.com<br />

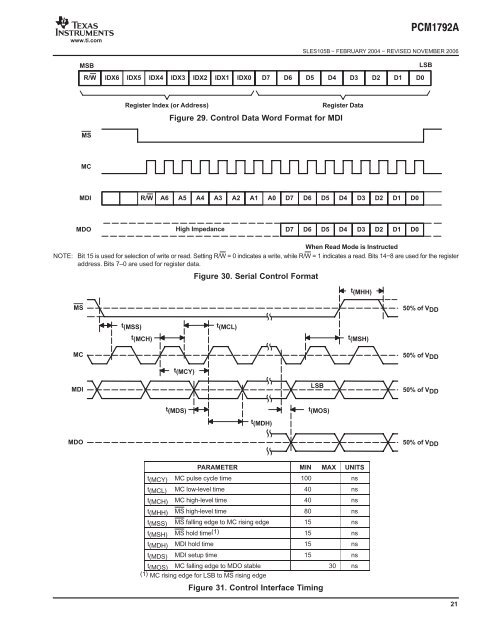

MSB<br />

Register Index (or Address) Register Data<br />

<br />

SLES105B − FEBRUARY 2004 − REVISED NOVEMBER 2006<br />

R/W IDX6 IDX5 IDX4 IDX3 IDX2 IDX1 IDX0 D7 D6 D5 D4 D3 D2 D1 D0<br />

MS<br />

MC<br />

MDI<br />

MDO<br />

Figure 29. Control Data Word Format for MDI<br />

R/W A6 A5 A4 A3 A2 A1<br />

High Impedance<br />

A0 D7 D6 D5 D4 D3 D2 D1 D0<br />

D7 D6 D5 D4 D3 D2 D1 D0<br />

When Read Mode is Instructed<br />

NOTE: <strong>Bit</strong> 15 is used for selection of write or read. Setting R/W = 0 indicates a write, while R/W = 1 indicates a read. <strong>Bit</strong>s 14−8 are used for the register<br />

address. <strong>Bit</strong>s 7–0 are used for register data.<br />

MS<br />

MC<br />

MDI<br />

MDO<br />

t(MSS)<br />

t(MCH)<br />

t(MCY)<br />

t(MDS)<br />

Figure 30. Serial Control Format<br />

t(MCL)<br />

t(MDH)<br />

LSB<br />

t(MOS)<br />

t(MHH)<br />

t(MSH)<br />

PARAMETER MIN MAX UNITS<br />

t(MCY) MC pulse cycle time 100 ns<br />

t(MCL) MC low-level time 40 ns<br />

t(MCH) MC high-level time 40 ns<br />

t(MHH) MS high-level time 80 ns<br />

t(MSS) MS falling edge to MC rising edge 15 ns<br />

t(MSH) MS hold time(1) 15 ns<br />

t(MDH) MDI hold time 15 ns<br />

t(MDS) MDI setup time 15 ns<br />

t(MOS) MC falling edge to MDO stable 30 ns<br />

(1) MC rising edge for LSB to MS rising edge<br />

Figure 31. Control Interface Timing<br />

LSB<br />

50% of VDD<br />

50% of VDD<br />

50% of VDD<br />

50% of VDD<br />

21