24-Bit, 192-kHz Sampling, Advanced Segment, Audio Stereo DAC ...

24-Bit, 192-kHz Sampling, Advanced Segment, Audio Stereo DAC ...

24-Bit, 192-kHz Sampling, Advanced Segment, Audio Stereo DAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

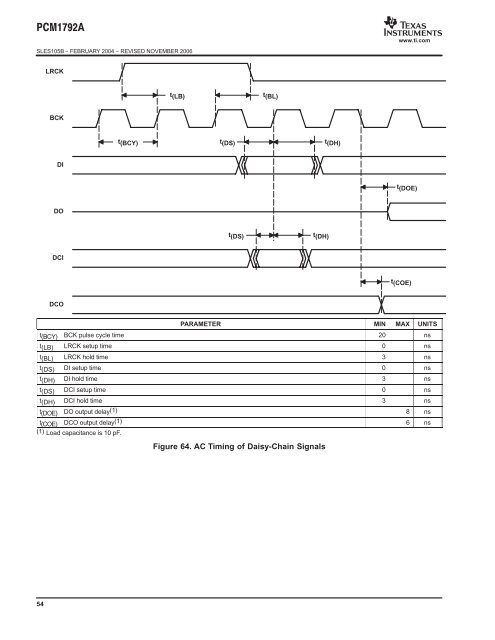

SLES105B − FEBRUARY 2004 − REVISED NOVEMBER 2006<br />

54<br />

LRCK<br />

BCK<br />

DI<br />

DO<br />

DCI<br />

DCO<br />

t(BCY)<br />

t(LB)<br />

t(DS)<br />

t(DS)<br />

t(BL)<br />

t(DH)<br />

t(DH)<br />

www.ti.com<br />

t(DOE)<br />

t(COE)<br />

PARAMETER MIN MAX UNITS<br />

t(BCY) BCK pulse cycle time 20 ns<br />

t(LB) LRCK setup time 0 ns<br />

t(BL) LRCK hold time 3 ns<br />

t(DS) DI setup time 0 ns<br />

t(DH) DI hold time 3 ns<br />

t(DS) DCI setup time 0 ns<br />

t(DH) DCI hold time 3 ns<br />

t(DOE) DO output delay(1) 8 ns<br />

t(COE) DCO output delay(1) 6 ns<br />

(1) Load capacitance is 10 pF.<br />

Figure 64. AC Timing of Daisy-Chain Signals