HyperLynx – High Speed PCB Design Workshop - RTP Designers ...

HyperLynx – High Speed PCB Design Workshop - RTP Designers ...

HyperLynx – High Speed PCB Design Workshop - RTP Designers ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

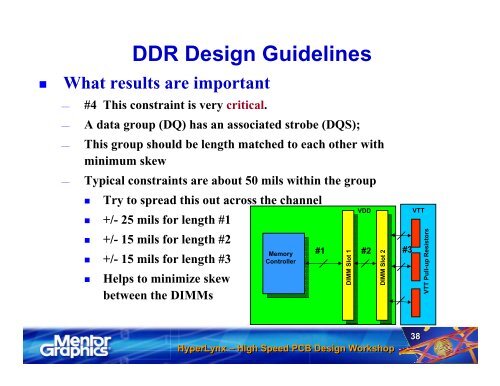

DDR <strong>Design</strong> Guidelines<br />

� What results are important<br />

— #4 This constraint is very critical.<br />

— A data group (DQ) has an associated strobe (DQS);<br />

— This group should be length matched to each other with<br />

minimum skew<br />

— Typical constraints are about 50 mils within the group<br />

� Try to spread this out across the channel<br />

� +/- 25 mils for length #1<br />

� +/- 15 mils for length #2<br />

� +/- 15 mils for length #3<br />

� Helps to minimize skew<br />

between the DIMMs<br />

Memory<br />

Controller<br />

<strong>HyperLynx</strong> <strong>–</strong> <strong>High</strong> <strong>Speed</strong> <strong>PCB</strong> <strong>Design</strong> <strong>Workshop</strong><br />

DIMM Slot 1<br />

VDD VTT<br />

#1 #2 #3<br />

DIMM Slot 2<br />

38<br />

VTT Pull-up Resistors