Implementing Audio IP in SDI II on Arria V Development Board - Altera

Implementing Audio IP in SDI II on Arria V Development Board - Altera

Implementing Audio IP in SDI II on Arria V Development Board - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

4<br />

Reference Design Comp<strong>on</strong>ents<br />

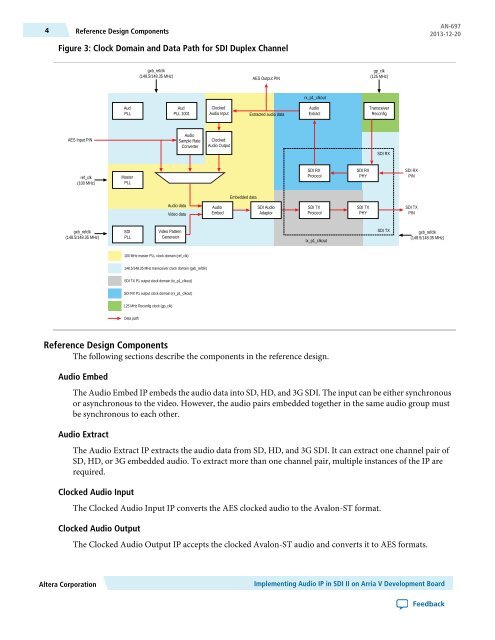

Figure 3: Clock Doma<str<strong>on</strong>g>in</str<strong>on</strong>g> and Data Path for <str<strong>on</strong>g>SDI</str<strong>on</strong>g> Duplex Channel<br />

AN-697<br />

2013-12-20<br />

gxb_refclk<br />

(148.5/148.35 MHz)<br />

AES Output PIN<br />

gp_clk<br />

(125 MHz)<br />

rx_p1_clkout<br />

Aud<br />

PLL<br />

Aud<br />

PLL 1001<br />

Clocked<br />

<str<strong>on</strong>g>Audio</str<strong>on</strong>g> Input<br />

Extracted audio data<br />

<str<strong>on</strong>g>Audio</str<strong>on</strong>g><br />

Extract<br />

Transceiver<br />

Rec<strong>on</strong>fig<br />

AES Input PIN<br />

<str<strong>on</strong>g>Audio</str<strong>on</strong>g><br />

Sample Rate<br />

C<strong>on</strong>verter<br />

Clocked<br />

<str<strong>on</strong>g>Audio</str<strong>on</strong>g> Output<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> RX<br />

ref_clk<br />

(100 MHz)<br />

Master<br />

PLL<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> RX<br />

Protocol<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> RX<br />

PHY<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> RX<br />

PIN<br />

Embedded data<br />

<str<strong>on</strong>g>Audio</str<strong>on</strong>g> data<br />

Video data<br />

<str<strong>on</strong>g>Audio</str<strong>on</strong>g><br />

Embed<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> <str<strong>on</strong>g>Audio</str<strong>on</strong>g><br />

Adaptor<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> TX<br />

Protocol<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> TX<br />

PHY<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> TX<br />

PIN<br />

gxb_refclk<br />

(148.5/148.35 MHz)<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g><br />

PLL<br />

Video Pattern<br />

Generator<br />

tx_p1_clkout<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> TX<br />

gxb_refclk<br />

(148.5/148.35 MHz)<br />

100 MHz master PLL clock doma<str<strong>on</strong>g>in</str<strong>on</strong>g> (ref_clk)<br />

148.5/148.35 MHz transceiver clock doma<str<strong>on</strong>g>in</str<strong>on</strong>g> (gxb_refclk)<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> TX P1 output clock doma<str<strong>on</strong>g>in</str<strong>on</strong>g> (tx_p1_clkout)<br />

<str<strong>on</strong>g>SDI</str<strong>on</strong>g> RX P1 output clock doma<str<strong>on</strong>g>in</str<strong>on</strong>g> (rx_p1_clkout)<br />

125 MHz Rec<strong>on</strong>fig clock (gp_clk)<br />

Data path<br />

Reference Design Comp<strong>on</strong>ents<br />

The follow<str<strong>on</strong>g>in</str<strong>on</strong>g>g secti<strong>on</strong>s describe the comp<strong>on</strong>ents <str<strong>on</strong>g>in</str<strong>on</strong>g> the reference design.<br />

<str<strong>on</strong>g>Audio</str<strong>on</strong>g> Embed<br />

The <str<strong>on</strong>g>Audio</str<strong>on</strong>g> Embed <str<strong>on</strong>g>IP</str<strong>on</strong>g> embeds the audio data <str<strong>on</strong>g>in</str<strong>on</strong>g>to SD, HD, and 3G <str<strong>on</strong>g>SDI</str<strong>on</strong>g>. The <str<strong>on</strong>g>in</str<strong>on</strong>g>put can be either synchr<strong>on</strong>ous<br />

or asynchr<strong>on</strong>ous to the video. However, the audio pairs embedded together <str<strong>on</strong>g>in</str<strong>on</strong>g> the same audio group must<br />

be synchr<strong>on</strong>ous to each other.<br />

<str<strong>on</strong>g>Audio</str<strong>on</strong>g> Extract<br />

The <str<strong>on</strong>g>Audio</str<strong>on</strong>g> Extract <str<strong>on</strong>g>IP</str<strong>on</strong>g> extracts the audio data from SD, HD, and 3G <str<strong>on</strong>g>SDI</str<strong>on</strong>g>. It can extract <strong>on</strong>e channel pair of<br />

SD, HD, or 3G embedded audio. To extract more than <strong>on</strong>e channel pair, multiple <str<strong>on</strong>g>in</str<strong>on</strong>g>stances of the <str<strong>on</strong>g>IP</str<strong>on</strong>g> are<br />

required.<br />

Clocked <str<strong>on</strong>g>Audio</str<strong>on</strong>g> Input<br />

The Clocked <str<strong>on</strong>g>Audio</str<strong>on</strong>g> Input <str<strong>on</strong>g>IP</str<strong>on</strong>g> c<strong>on</strong>verts the AES clocked audio to the Aval<strong>on</strong>-ST format.<br />

Clocked <str<strong>on</strong>g>Audio</str<strong>on</strong>g> Output<br />

The Clocked <str<strong>on</strong>g>Audio</str<strong>on</strong>g> Output <str<strong>on</strong>g>IP</str<strong>on</strong>g> accepts the clocked Aval<strong>on</strong>-ST audio and c<strong>on</strong>verts it to AES formats.<br />

<strong>Altera</strong> Corporati<strong>on</strong><br />

<str<strong>on</strong>g>Implement<str<strong>on</strong>g>in</str<strong>on</strong>g>g</str<strong>on</strong>g> <str<strong>on</strong>g>Audio</str<strong>on</strong>g> <str<strong>on</strong>g>IP</str<strong>on</strong>g> <str<strong>on</strong>g>in</str<strong>on</strong>g> <str<strong>on</strong>g>SDI</str<strong>on</strong>g> <str<strong>on</strong>g>II</str<strong>on</strong>g> <strong>on</strong> <strong>Arria</strong> V <strong>Development</strong> <strong>Board</strong><br />

Feedback