Implementing Audio IP in SDI II on Arria V Development Board - Altera

Implementing Audio IP in SDI II on Arria V Development Board - Altera

Implementing Audio IP in SDI II on Arria V Development Board - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

AN-697<br />

2013-12-20<br />

Runn<str<strong>on</strong>g>in</str<strong>on</strong>g>g the Reference Design<br />

9<br />

• D<str<strong>on</strong>g>IP</str<strong>on</strong>g> Switch Bank<br />

• JTAG Cha<str<strong>on</strong>g>in</str<strong>on</strong>g> Header Switch C<strong>on</strong>trols<br />

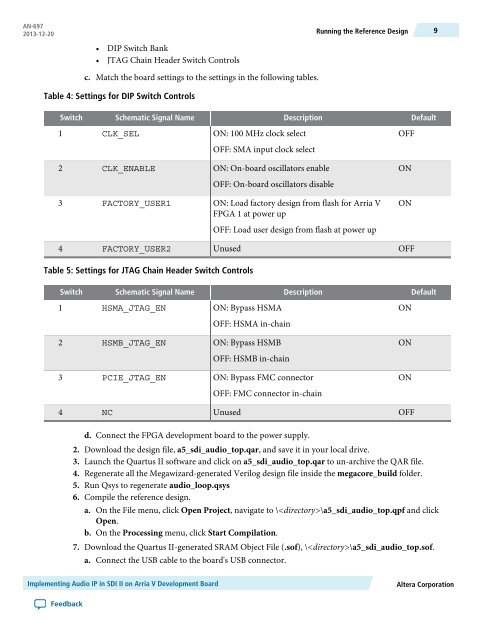

c. Match the board sett<str<strong>on</strong>g>in</str<strong>on</strong>g>gs to the sett<str<strong>on</strong>g>in</str<strong>on</strong>g>gs <str<strong>on</strong>g>in</str<strong>on</strong>g> the follow<str<strong>on</strong>g>in</str<strong>on</strong>g>g tables.<br />

Table 4: Sett<str<strong>on</strong>g>in</str<strong>on</strong>g>gs for D<str<strong>on</strong>g>IP</str<strong>on</strong>g> Switch C<strong>on</strong>trols<br />

Switch<br />

Schematic Signal Name<br />

Descripti<strong>on</strong><br />

Default<br />

1<br />

CLK_SEL<br />

ON: 100 MHz clock select<br />

OFF<br />

OFF: SMA <str<strong>on</strong>g>in</str<strong>on</strong>g>put clock select<br />

2<br />

CLK_ENABLE<br />

ON: On-board oscillators enable<br />

ON<br />

OFF: On-board oscillators disable<br />

3<br />

FACTORY_USER1<br />

ON: Load factory design from flash for <strong>Arria</strong> V<br />

FPGA 1 at power up<br />

ON<br />

OFF: Load user design from flash at power up<br />

4<br />

FACTORY_USER2<br />

Unused<br />

OFF<br />

Table 5: Sett<str<strong>on</strong>g>in</str<strong>on</strong>g>gs for JTAG Cha<str<strong>on</strong>g>in</str<strong>on</strong>g> Header Switch C<strong>on</strong>trols<br />

Switch<br />

Schematic Signal Name<br />

Descripti<strong>on</strong><br />

Default<br />

1<br />

HSMA_JTAG_EN<br />

ON: Bypass HSMA<br />

ON<br />

OFF: HSMA <str<strong>on</strong>g>in</str<strong>on</strong>g>-cha<str<strong>on</strong>g>in</str<strong>on</strong>g><br />

2<br />

HSMB_JTAG_EN<br />

ON: Bypass HSMB<br />

ON<br />

OFF: HSMB <str<strong>on</strong>g>in</str<strong>on</strong>g>-cha<str<strong>on</strong>g>in</str<strong>on</strong>g><br />

3<br />

PCIE_JTAG_EN<br />

ON: Bypass FMC c<strong>on</strong>nector<br />

ON<br />

OFF: FMC c<strong>on</strong>nector <str<strong>on</strong>g>in</str<strong>on</strong>g>-cha<str<strong>on</strong>g>in</str<strong>on</strong>g><br />

4<br />

NC<br />

Unused<br />

OFF<br />

d. C<strong>on</strong>nect the FPGA development board to the power supply.<br />

2. Download the design file, a5_sdi_audio_top.qar, and save it <str<strong>on</strong>g>in</str<strong>on</strong>g> your local drive.<br />

3. Launch the Quartus <str<strong>on</strong>g>II</str<strong>on</strong>g> software and click <strong>on</strong> a5_sdi_audio_top.qar to un-archive the QAR file.<br />

4. Regenerate all the Megawizard-generated Verilog design file <str<strong>on</strong>g>in</str<strong>on</strong>g>side the megacore_build folder.<br />

5. Run Qsys to regenerate audio_loop.qsys<br />

6. Compile the reference design.<br />

a. On the File menu, click Open Project, navigate to \\a5_sdi_audio_top.qpf and click<br />

Open.<br />

b. On the Process<str<strong>on</strong>g>in</str<strong>on</strong>g>g menu, click Start Compilati<strong>on</strong>.<br />

7. Download the Quartus <str<strong>on</strong>g>II</str<strong>on</strong>g>-generated SRAM Object File (.sof), \\a5_sdi_audio_top.sof.<br />

a. C<strong>on</strong>nect the USB cable to the board's USB c<strong>on</strong>nector.<br />

<str<strong>on</strong>g>Implement<str<strong>on</strong>g>in</str<strong>on</strong>g>g</str<strong>on</strong>g> <str<strong>on</strong>g>Audio</str<strong>on</strong>g> <str<strong>on</strong>g>IP</str<strong>on</strong>g> <str<strong>on</strong>g>in</str<strong>on</strong>g> <str<strong>on</strong>g>SDI</str<strong>on</strong>g> <str<strong>on</strong>g>II</str<strong>on</strong>g> <strong>on</strong> <strong>Arria</strong> V <strong>Development</strong> <strong>Board</strong><br />

<strong>Altera</strong> Corporati<strong>on</strong><br />

Feedback