LDPC Decoding: VLSI Architectures and Implementations

LDPC Decoding: VLSI Architectures and Implementations

LDPC Decoding: VLSI Architectures and Implementations

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

κ<br />

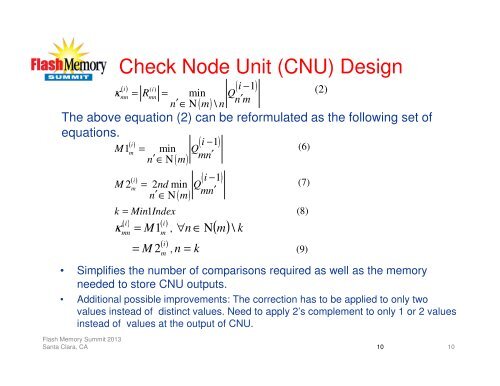

Check Node Unit (CNU) Design<br />

( i)<br />

mn<br />

The above equation (2) can be reformulated as the following set of<br />

equations.<br />

( i)<br />

M1m<br />

= min<br />

n′∈ Ν<br />

( i)<br />

( m)<br />

( m)<br />

( i −1)<br />

Q mn ′<br />

( i −1)<br />

M 2m<br />

= 2nd min Q<br />

n′∈ Ν mn ′<br />

• Simplifies the number of comparisons required as well as the memory<br />

needed to store CNU outputs.<br />

• Additional possible improvements: The correction has to be applied to only two<br />

values instead of distinct values. Need to apply 2’s complement to only 1 or 2 values<br />

instead of values at the output of CNU.<br />

Flash Memory Summit 2013<br />

Santa Clara, CA 10<br />

10<br />

(6)<br />

(7)<br />

k = Min1Index<br />

(8)<br />

( i) ( i)<br />

mn<br />

M1<br />

κ = , ∀ n ∈ Ν( m) \ k<br />

m<br />

( )<br />

( i − )<br />

= R = min Q<br />

n′∈ Ν m \ n n ′ m<br />

( i) 1<br />

mn<br />

( )<br />

= M 2 i m<br />

, n = k<br />

(9)<br />

(2)