LDPC Decoding: VLSI Architectures and Implementations

LDPC Decoding: VLSI Architectures and Implementations

LDPC Decoding: VLSI Architectures and Implementations

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

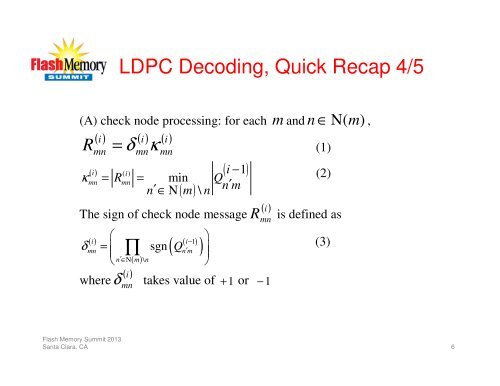

<strong>LDPC</strong> <strong>Decoding</strong>, Quick Recap 4/5<br />

(A) check node processing: for each m <strong>and</strong> n Ν(m)<br />

R<br />

κ<br />

( i)<br />

mn<br />

∈ ,<br />

( i) ( i) ( i)<br />

= δ κ<br />

(1)<br />

mn<br />

mn<br />

= R =<br />

mn<br />

( )<br />

( i − )<br />

min Q<br />

n′∈ Ν m \ n n ′ m<br />

( i) 1<br />

mn<br />

The sign of check node message<br />

(2)<br />

( i )<br />

R is defined as<br />

mn<br />

( )<br />

⎛<br />

( )<br />

⎞<br />

i<br />

i−1<br />

δmn<br />

= ⎜<br />

⎟<br />

⎝ n′∈Ν<br />

( m)<br />

\ n ⎠<br />

( i)<br />

whereδ takes value of + 1 or − 1<br />

sgn ( Q )<br />

(3)<br />

∏ n′<br />

m<br />

mn<br />

Flash Memory Summit 2013<br />

Santa Clara, CA 6