LDPC Decoding: VLSI Architectures and Implementations

LDPC Decoding: VLSI Architectures and Implementations

LDPC Decoding: VLSI Architectures and Implementations

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

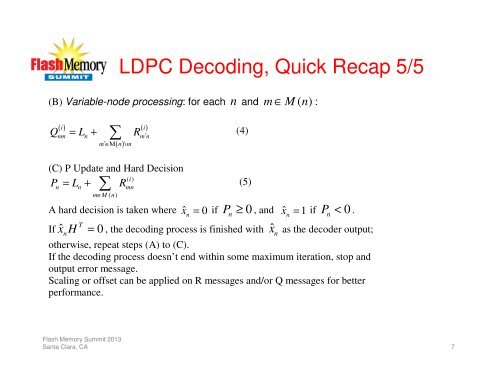

<strong>LDPC</strong> <strong>Decoding</strong>, Quick Recap 5/5<br />

(B) Variable-node processing: for each n <strong>and</strong> m M ( n)<br />

( i) ( i)<br />

Q = L + ∑ R ′<br />

(4)<br />

nm n m n<br />

m′∈Μ<br />

( n)\<br />

m<br />

(C) P Update <strong>and</strong> Hard Decision<br />

( i)<br />

P = L + ∑ R<br />

(5)<br />

n n mn<br />

m∈M ( n)<br />

∈ :<br />

A hard decision is taken where x ˆn<br />

= 0 if Pn<br />

≥ 0 , <strong>and</strong> x ˆn<br />

= 1 if P<br />

n<br />

< 0 .<br />

T<br />

If xˆ nH = 0 , the decoding process is finished with x ˆn<br />

as the decoder output;<br />

otherwise, repeat steps (A) to (C).<br />

If the decoding process doesn’t end within some maximum iteration, stop <strong>and</strong><br />

output error message.<br />

Scaling or offset can be applied on R messages <strong>and</strong>/or Q messages for better<br />

performance.<br />

Flash Memory Summit 2013<br />

Santa Clara, CA 7