LDPC Decoding: VLSI Architectures and Implementations

LDPC Decoding: VLSI Architectures and Implementations

LDPC Decoding: VLSI Architectures and Implementations

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

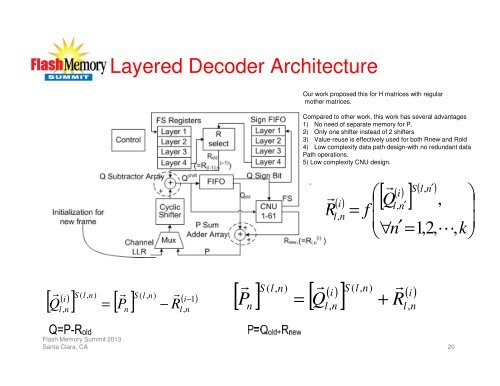

Layered Decoder Architecture<br />

Our work proposed this for H matrices with regular<br />

mother matrices.<br />

Compared to other work, this work has several advantages<br />

1) No need of separate memory for P.<br />

2) Only one shifter instead of 2 shifters<br />

3) Value-reuse is effectively used for both Rnew <strong>and</strong> Rold<br />

4) Low complexity data path design-with no redundant data<br />

Path operations.<br />

5) Low complexity CNU design.<br />

r<br />

R<br />

( i)<br />

l,<br />

n<br />

=<br />

⎛<br />

f ⎜<br />

⎜<br />

⎝<br />

r<br />

[<br />

( )<br />

] ( ′<br />

i<br />

S l,<br />

n<br />

Q<br />

) ⎟ ⎟ ⎞<br />

l,<br />

n′<br />

,<br />

∀ n′<br />

= 1,2, L,<br />

k⎠<br />

r<br />

[<br />

( )] [ ]<br />

i<br />

S ( l,<br />

n)<br />

S ( l,<br />

n)<br />

( i−1)<br />

Q = P − R<br />

l,<br />

n<br />

r<br />

n<br />

r<br />

l,<br />

n<br />

r<br />

r ( r<br />

P<br />

n<br />

l,<br />

n<br />

l,<br />

n<br />

[ ]<br />

S l,<br />

n)<br />

[<br />

( )] i<br />

S ( l,<br />

n)<br />

( i)<br />

= Q + R<br />

Q=P-Rold<br />

Flash Memory Summit 2013<br />

Santa Clara, CA 20