Content

Content

Content

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

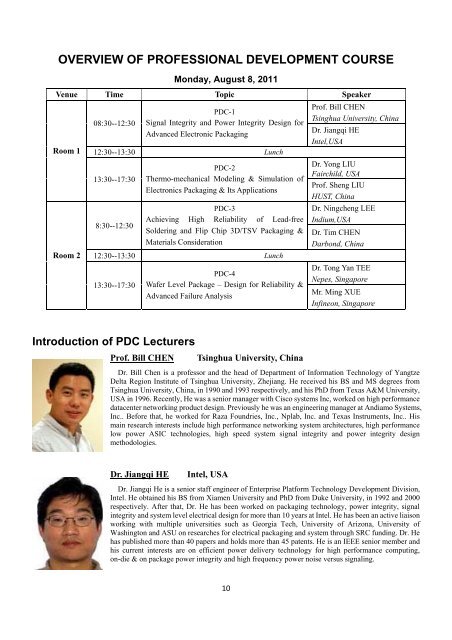

OVERVIEW OF PROFESSIONAL DEVELOPMENT COURSE<br />

Monday, August 8, 2011<br />

Venue Time Topic Speaker<br />

Room 1<br />

Room 2<br />

08:30--12:30<br />

PDC-1<br />

Signal Integrity and Power Integrity Design for<br />

Advanced Electronic Packaging<br />

12:30--13:30 Lunch<br />

13:30--17:30<br />

PDC-2<br />

Thermo-mechanical Modeling & Simulation of<br />

Electronics Packaging & Its Applications<br />

PDC-3<br />

Achieving High Reliability of Lead-free<br />

8:30--12:30<br />

Soldering and Flip Chip 3D/TSV Packaging &<br />

Materials Consideration<br />

12:30--13:30 Lunch<br />

13:30--17:30<br />

PDC-4<br />

Wafer Level Package – Design for Reliability &<br />

Advanced Failure Analysis<br />

Prof. Bill CHEN<br />

Tsinghua University, China<br />

Dr. Jiangqi HE<br />

Intel,USA<br />

Dr. Yong LIU<br />

Fairchild, USA<br />

Prof. Sheng LIU<br />

HUST, China<br />

Dr. Ningcheng LEE<br />

Indium,USA<br />

Dr. Tim CHEN<br />

Darbond, China<br />

Dr. Tong Yan TEE<br />

Nepes, Singapore<br />

Mr. Ming XUE<br />

Infineon, Singapore<br />

Introduction of PDC Lecturers<br />

Prof. Bill CHEN<br />

Tsinghua University, China<br />

Dr. Bill Chen is a professor and the head of Department of Information Technology of Yangtze<br />

Delta Region Institute of Tsinghua University, Zhejiang. He received his BS and MS degrees from<br />

Tsinghua University, China, in 1990 and 1993 respectively, and his PhD from Texas A&M University,<br />

USA in 1996. Recently, He was a senior manager with Cisco systems Inc, worked on high performance<br />

datacenter networking product design. Previously he was an engineering manager at Andiamo Systems,<br />

Inc.. Before that, he worked for Raza Foundries, Inc., Nplab, Inc. and Texas Instruments, Inc.. His<br />

main research interests include high performance networking system architectures, high performance<br />

low power ASIC technologies, high speed system signal integrity and power integrity design<br />

methodologies.<br />

Dr. Jiangqi HE<br />

Intel, USA<br />

Dr. Jiangqi He is a senior staff engineer of Enterprise Platform Technology Development Division,<br />

Intel. He obtained his BS from Xiamen University and PhD from Duke University, in 1992 and 2000<br />

respectively. After that, Dr. He has been worked on packaging technology, power integrity, signal<br />

integrity and system level electrical design for more than 10 years at Intel. He has been an active liaison<br />

working with multiple universities such as Georgia Tech, University of Arizona, University of<br />

Washington and ASU on researches for electrical packaging and system through SRC funding. Dr. He<br />

has published more than 40 papers and holds more than 45 patents. He is an IEEE senior member and<br />

his current interests are on efficient power delivery technology for high performance computing,<br />

on-die & on package power integrity and high frequency power noise versus signaling.<br />

10