Content

Content

Content

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

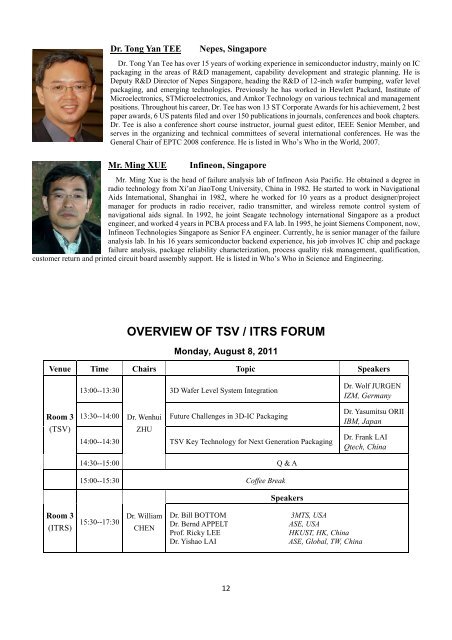

Dr. Tong Yan TEE<br />

Nepes, Singapore<br />

Dr. Tong Yan Tee has over 15 years of working experience in semiconductor industry, mainly on IC<br />

packaging in the areas of R&D management, capability development and strategic planning. He is<br />

Deputy R&D Director of Nepes Singapore, heading the R&D of 12-inch wafer bumping, wafer level<br />

packaging, and emerging technologies. Previously he has worked in Hewlett Packard, Institute of<br />

Microelectronics, STMicroelectronics, and Amkor Technology on various technical and management<br />

positions. Throughout his career, Dr. Tee has won 13 ST Corporate Awards for his achievement, 2 best<br />

paper awards, 6 US patents filed and over 150 publications in journals, conferences and book chapters.<br />

Dr. Tee is also a conference short course instructor, journal guest editor, IEEE Senior Member, and<br />

serves in the organizing and technical committees of several international conferences. He was the<br />

General Chair of EPTC 2008 conference. He is listed in Who’s Who in the World, 2007.<br />

Mr. Ming XUE<br />

Infineon, Singapore<br />

Mr. Ming Xue is the head of failure analysis lab of Infineon Asia Pacific. He obtained a degree in<br />

radio technology from Xi’an JiaoTong University, China in 1982. He started to work in Navigational<br />

Aids International, Shanghai in 1982, where he worked for 10 years as a product designer/project<br />

manager for products in radio receiver, radio transmitter, and wireless remote control system of<br />

navigational aids signal. In 1992, he joint Seagate technology international Singapore as a product<br />

engineer, and worked 4 years in PCBA process and FA lab. In 1995, he joint Siemens Component, now,<br />

Infineon Technologies Singapore as Senior FA engineer. Currently, he is senior manager of the failure<br />

analysis lab. In his 16 years semiconductor backend experience, his job involves IC chip and package<br />

failure analysis, package reliability characterization, process quality risk management, qualification,<br />

customer return and printed circuit board assembly support. He is listed in Who’s Who in Science and Engineering.<br />

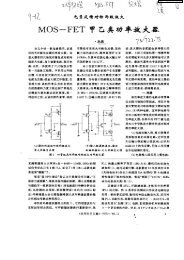

OVERVIEW OF TSV / ITRS FORUM<br />

Monday, August 8, 2011<br />

Venue Time Chairs Topic Speakers<br />

Room 3<br />

(TSV)<br />

13:00--13:30 3D Wafer Level System Integration<br />

13:30--14:00 Dr. Wenhui Future Challenges in 3D-IC Packaging<br />

ZHU<br />

14:00--14:30 TSV Key Technology for Next Generation Packaging<br />

Dr. Wolf JURGEN<br />

IZM, Germany<br />

Dr. Yasumitsu ORII<br />

IBM, Japan<br />

Dr. Frank LAI<br />

Qtech, China<br />

14:30--15:00<br />

Q & A<br />

15:00--15:30 Coffee Break<br />

Speakers<br />

Room 3<br />

(ITRS)<br />

15:30--17:30<br />

Dr. William<br />

CHEN<br />

Dr. Bill BOTTOM<br />

Dr. Bernd APPELT<br />

Prof. Ricky LEE<br />

Dr. Yishao LAI<br />

3MTS, USA<br />

ASE, USA<br />

HKUST, HK, China<br />

ASE, Global, TW, China<br />

12