Military Embedded Systems Summer 2006

Military Embedded Systems Summer 2006

Military Embedded Systems Summer 2006

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Hardware<br />

Reconfigurable FPGAs<br />

Local Link is a packet-oriented interface<br />

for streaming data applications. In a DSP<br />

application, it is common for sensor data<br />

– digitized RF, electro-optical, and sonar<br />

– to arrive in nonaddressed packet form.<br />

The RocketIO controllers (3.125 Gbps)<br />

are supported with Local Link interfaces<br />

and DMA controllers to direct streaming<br />

data into memory-addressed locations.<br />

To simplify the interconnection of user IP<br />

with the toolkit IP modules, the company<br />

has developed an IPIC switch, which<br />

allows modules with IPIC or Local Link<br />

interfaces to connect together seamlessly<br />

(see Figure 3). Multiple IPIC switches<br />

can be instantiated in the design, allowing<br />

users flexibility in choosing the best<br />

solution.<br />

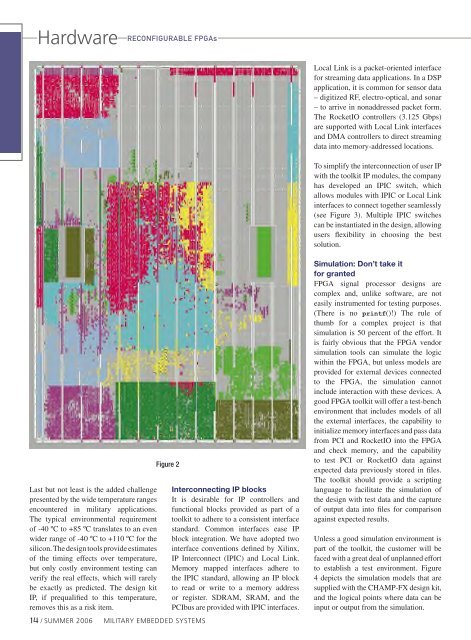

Last but not least is the added challenge<br />

presented by the wide temperature ranges<br />

encountered in military applications.<br />

The typical environmental requirement<br />

of -40 ºC to +85 ºC translates to an even<br />

wider range of -40 ºC to +110 ºC for the<br />

silicon. The design tools provide estimates<br />

of the timing effects over temperature,<br />

but only costly environment testing can<br />

verify the real effects, which will rarely<br />

be exactly as predicted. The design kit<br />

IP, if prequalified to this temperature,<br />

removes this as a risk item.<br />

Figure 2<br />

14 / SUMMER <strong>2006</strong> <strong>Military</strong> EMBEDDED SYSTEMS<br />

Interconnecting IP blocks<br />

It is desirable for IP controllers and<br />

functional blocks provided as part of a<br />

toolkit to adhere to a consistent interface<br />

standard. Common interfaces ease IP<br />

block integration. We have adopted two<br />

interface conventions defined by Xilinx,<br />

IP Interconnect (IPIC) and Local Link.<br />

Memory mapped interfaces adhere to<br />

the IPIC standard, allowing an IP block<br />

to read or write to a memory address<br />

or register. SDRAM, SRAM, and the<br />

PCIbus are provided with IPIC interfaces.<br />

Simulation: Don’t take it<br />

for granted<br />

FPGA signal processor designs are<br />

complex and, unlike software, are not<br />

easily instrumented for testing purposes.<br />

(There is no printf()!) The rule of<br />

thumb for a complex project is that<br />

simulation is 50 percent of the effort. It<br />

is fairly obvious that the FPGA vendor<br />

simulation tools can simulate the logic<br />

within the FPGA, but unless models are<br />

provided for external devices connected<br />

to the FPGA, the simulation cannot<br />

include interaction with these devices. A<br />

good FPGA toolkit will offer a test-bench<br />

environment that includes models of all<br />

the external interfaces, the capability to<br />

initialize memory interfaces and pass data<br />

from PCI and RocketIO into the FPGA<br />

and check memory, and the capability<br />

to test PCI or RocketIO data against<br />

expected data previously stored in files.<br />

The toolkit should provide a scripting<br />

language to facilitate the simulation of<br />

the design with test data and the capture<br />

of output data into files for comparison<br />

against expected results.<br />

Unless a good simulation environment is<br />

part of the toolkit, the customer will be<br />

faced with a great deal of unplanned effort<br />

to establish a test environment. Figure<br />

4 depicts the simulation models that are<br />

supplied with the CHAMP-FX design kit,<br />

and the logical points where data can be<br />

input or output from the simulation.