Military Embedded Systems Summer 2006

Military Embedded Systems Summer 2006

Military Embedded Systems Summer 2006

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Reconfigurable FPGAs<br />

Hardware<br />

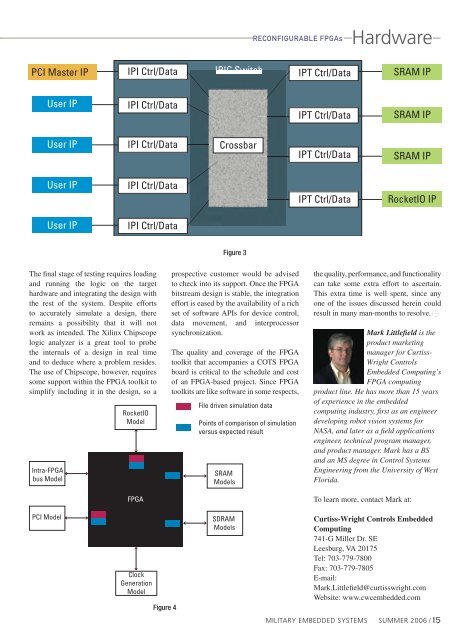

PCI Master IP<br />

IPI Ctrl/Data<br />

IPIC Switch<br />

IPT Ctrl/Data<br />

SRAM User IP IP<br />

User IP<br />

IPI Ctrl/Data<br />

IPT Ctrl/Data<br />

SRAM User IP IP<br />

User IP<br />

IPI Ctrl/Data<br />

Crossbar<br />

IPT Ctrl/Data<br />

SRAM User IP IP<br />

User IP<br />

IPI Ctrl/Data<br />

IPT Ctrl/Data<br />

RocketIO User IP IP<br />

User IP<br />

IPI Ctrl/Data<br />

Figure 3<br />

The final stage of testing requires loading<br />

and running the logic on the target<br />

hardware and integrating the design with<br />

the rest of the system. Despite efforts<br />

to accurately simulate a design, there<br />

remains a possibility that it will not<br />

work as intended. The Xilinx Chipscope<br />

logic analyzer is a great tool to probe<br />

the internals of a design in real time<br />

and to deduce where a problem resides.<br />

The use of Chipscope, however, requires<br />

some support within the FPGA toolkit to<br />

simplify including it in the design, so a<br />

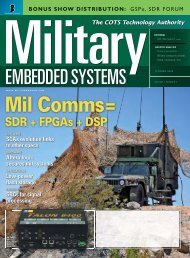

Intra-FPGA<br />

bus Model<br />

RocketIO<br />

Model<br />

FPGA<br />

prospective customer would be advised<br />

to check into its support. Once the FPGA<br />

bitstream design is stable, the integration<br />

effort is eased by the availability of a rich<br />

set of software APIs for device control,<br />

data movement, and interprocessor<br />

synchronization.<br />

The quality and coverage of the FPGA<br />

toolkit that accompanies a COTS FPGA<br />

board is critical to the schedule and cost<br />

of an FPGA-based project. Since FPGA<br />

toolkits are like software in some respects,<br />

File driven simulation data<br />

Points of comparison of simulation<br />

versus expected result<br />

SRAM<br />

Models<br />

the quality, performance, and functionality<br />

can take some extra effort to ascertain.<br />

This extra time is well spent, since any<br />

one of the issues discussed herein could<br />

result in many man-months to resolve.<br />

Mark Littlefield is the<br />

product marketing<br />

manager for Curtiss-<br />

Wright Controls<br />

<strong>Embedded</strong> Computing’s<br />

FPGA computing<br />

product line. He has more than 15 years<br />

of experience in the embedded<br />

computing industry, first as an engineer<br />

developing robot vision systems for<br />

NASA, and later as a field applications<br />

engineer, technical program manager,<br />

and product manager. Mark has a BS<br />

and an MS degree in Control <strong>Systems</strong><br />

Engineering from the University of West<br />

Florida.<br />

To learn more, contact Mark at:<br />

PCI Model<br />

Clock<br />

Generation<br />

Model<br />

Figure 4<br />

SDRAM<br />

Models<br />

Curtiss-Wright Controls <strong>Embedded</strong><br />

Computing<br />

741-G Miller Dr. SE<br />

Leesburg, VA 20175<br />

Tel: 703-779-7800<br />

Fax: 703-779-7805<br />

E-mail:<br />

Mark.Littlefield@curtisswright.com<br />

Website: www.cwcembedded.com<br />

<strong>Military</strong> EMBEDDED SYSTEMS SUMMER <strong>2006</strong> / 15