TetraMAX ATPG - Europractice

TetraMAX ATPG - Europractice

TetraMAX ATPG - Europractice

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

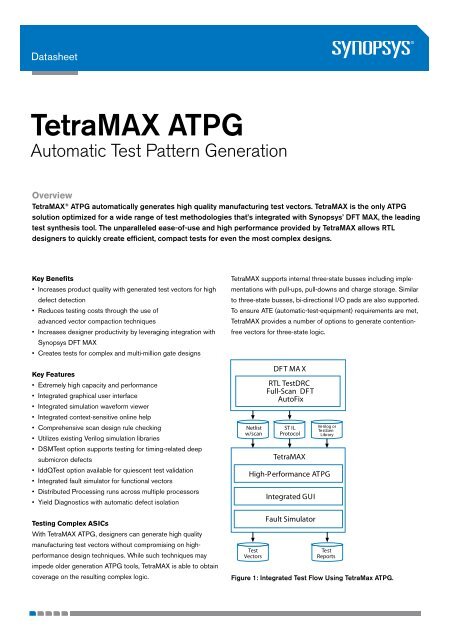

Datasheet<strong>TetraMAX</strong> <strong>ATPG</strong>Automatic Test Pattern GenerationOverview<strong>TetraMAX</strong> ® <strong>ATPG</strong> automatically generates high quality manufacturing test vectors. <strong>TetraMAX</strong> is the only <strong>ATPG</strong>solution optimized for a wide range of test methodologies that’s integrated with Synopsys’ DFT MAX, the leadingtest synthesis tool. The unparalleled ease-of-use and high performance provided by <strong>TetraMAX</strong> allows RTLdesigners to quickly create efficient, compact tests for even the most complex designs.Key Benefits• Increases product quality with generated test vectors for highdefect detection• Reduces testing costs through the use ofadvanced vector compaction techniques• Increases designer productivity by leveraging integration withSynopsys DFT MAX• Creates tests for complex and multi-million gate designsKey Features• Extremely high capacity and performance• Integrated graphical user interface• Integrated simulation waveform viewer• Integrated context-sensitive online help• Comprehensive scan design rule checking• Utilizes existing Verilog simulation libraries• DSMTest option supports testing for timing-related deepsubmicron defects• IddQTest option available for quiescent test validation• Integrated fault simulator for functional vectors• Distributed Processing runs across multiple processors• Yield Diagnostics with automatic defect isolationTesting Complex ASICsWith <strong>TetraMAX</strong> <strong>ATPG</strong>, designers can generate high qualitymanufacturing test vectors without compromising on highperformancedesign techniques. While such techniques mayimpede older generation <strong>ATPG</strong> tools, <strong>TetraMAX</strong> is able to obtaincoverage on the resulting complex logic.<strong>TetraMAX</strong> supports internal three-state busses including implementationswith pull-ups, pull-downs and charge storage. Similarto three-state busses, bi-directional I/O pads are also supported.To ensure ATE (automatic-test-equipment) requirements are met,<strong>TetraMAX</strong> provides a number of options to generate contentionfreevectors for three-state logic.Netlistw/scanHigh-Performance <strong>ATPG</strong>TestVectorsDFT MA XRTL TestDRCFull-Scan DFTAutoFixST ILProtocol<strong>TetraMAX</strong>Integrated GUIFault SimulatorVerilog orTestGenLibraryTestReportsFigure 1: Integrated Test Flow Using TetraMax <strong>ATPG</strong>.

<strong>TetraMAX</strong> <strong>ATPG</strong>Figure 4: <strong>TetraMAX</strong> Provides High-Performance <strong>ATPG</strong>and Advanced Debug Capabilities through its IntegratedGraphical Interfaces.Figure 5: <strong>TetraMAX</strong> DelayTest Automates testing of CriticalPaths.physical defects that create a conduction path from the powersupply to ground and result in excessive current draw.<strong>TetraMAX</strong> generates a minimal set of high fault coverage vectorsfor IDDQ testing purposes, and constrains the test vectors toavoid excessive current during the quiescent state. The <strong>TetraMAX</strong>IddQTest option then accurately validates these vectors for lowquiescence using Synopsys VCS or other Verilog simulator,thereby ensuring the IDDQ vectors will work on the ATE.Distributed ProcessingFor very large designs, the <strong>TetraMAX</strong> TenX option enables <strong>ATPG</strong>and fault simulation to be run across multiple processors. TheTenX distributed processing architecture is highly scalable toover 10 processors, and compared to a single processor cangenerate test vectors in less than 1/10th time but with the samehigh test coverage and minimal vector counts. The TenX optionsupports networks with heterogeneous platforms and popularcompute management applications such as LSF.Yield DiagnosticsIn addition to identifying defective parts from manufacturing,<strong>TetraMAX</strong> <strong>ATPG</strong> can also isolate the location of defects ondevices that fail <strong>TetraMAX</strong> test vectors. Automatic andaccurate defect isolation is an important step to diagnose criticalyield issues, both during production ramp as well as in volumemanufacturing. <strong>TetraMAX</strong> diagnostics read the test vectors andtester failure data, which are the differences between measuredand expected responses to those test vectors, and report thefault candidate locations that most likely explain the faulty devicebehavior observed on the tester. <strong>TetraMAX</strong> diagnostics useadvanced heuristics and a high performance fault simulator forrapid and reliable results in a volume manufacturing environment.Netlist Formats, Testbenches, and Test Vectors Interfaces<strong>TetraMAX</strong> supports popular industry standards for netlist and testvector formats:Circuit netlist: Verilog, VHDL (87 and 93)Library: Verilog functional (Structural and UDPs)Testbench: Verilog (serial and parallel), VHDL-93(serial only)Test vectors: STIL, WGL, Toshiba TSTL2,Texas Instruments TDL91, Fujitsu FTDL,and Verilog VCDE (input only)For more information about Synopsys products, supportservices or training, visit us on the web at: www.synopsys.com,contact your local sales representative or call650.584.5000.Synopsys, Inc.700 East Middlefield RoadMountain View, CA 94043www.synopsys.com©2006 Synopsys, Inc. Synopsys, the Synopsys logo, DesignWare, VCS and Vera are registered trademarks and Design Compiler and OpenVera are trademarks of Synopsys, Inc.PCI Express, PCI-X, PCI and PCI-SIG are registered trademarks of PCI-SIG. All other products orservice names mentioned herein are trademarksof their respective holders and should be treated as such. Printed in the U.S.A. ©2006 Synopsys, Inc. 05/06.CE.06-14476