Cadence VIP Catalog - Europractice

Cadence VIP Catalog - Europractice

Cadence VIP Catalog - Europractice

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

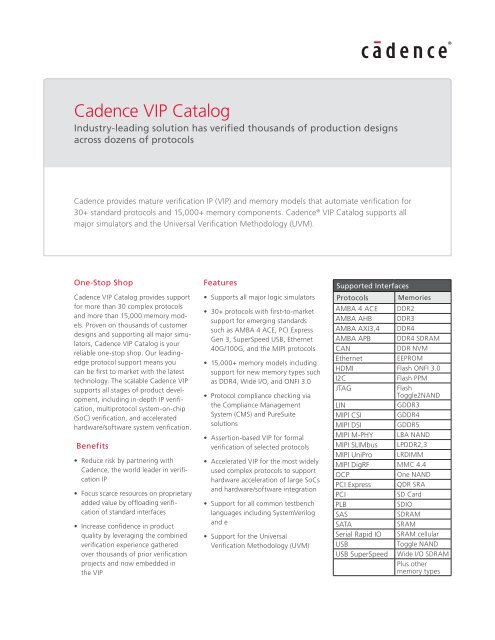

<strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong>Industry-leading solution has verified thousands of production designsacross dozens of protocols<strong>Cadence</strong> provides mature verification IP (<strong>VIP</strong>) and memory models that automate verification for30+ standard protocols and 15,000+ memory components. <strong>Cadence</strong> ® <strong>VIP</strong> <strong>Catalog</strong> supports allmajor simulators and the Universal Verification Methodology (UVM).One-Stop Shop<strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong> provides supportfor more than 30 complex protocolsand more than 15,000 memory models.Proven on thousands of customerdesigns and supporting all major simulators,<strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong> is yourreliable one-stop shop. Our leadingedgeprotocol support means youcan be first to market with the latesttechnology. The scalable <strong>Cadence</strong> <strong>VIP</strong>supports all stages of product development,including in-depth IP verification,multiprotocol system-on-chip(SoC) verification, and acceleratedhardware/software system verification.Benefits• Reduce risk by partnering with<strong>Cadence</strong>, the world leader in verificationIP• Focus scarce resources on proprietaryadded value by offloading verificationof standard interfaces• Increase confidence in productquality by leveraging the combinedverification experience gatheredover thousands of prior verificationprojects and now embedded inthe <strong>VIP</strong>Features• Supports all major logic simulators• 30+ protocols with first-to-marketsupport for emerging standardssuch as AMBA 4 ACE, PCI ExpressGen 3, SuperSpeed USB, Ethernet40G/100G, and the MIPI protocols• 15,000+ memory models includingsupport for new memory types suchas DDR4, Wide I/O, and ONFI 3.0• Protocol compliance checking viathe Compliance ManagementSystem (CMS) and PureSuitesolutions• Assertion-based <strong>VIP</strong> for formalverification of selected protocols• Accelerated <strong>VIP</strong> for the most widelyused complex protocols to supporthardware acceleration of large SoCsand hardware/software integration• Support for all common testbenchlanguages including SystemVerilogand e• Support for the UniversalVerification Methodology (UVM)Supported InterfacesProtocols MemoriesAMBA 4 ACE DDR2AMBA AHB DDR3AMBA AXI3,4 DDR4AMBA APB DDR4 SDRAMCANDDR NVMEthernetEEPROMHDMI Flash ONFI 3.0I2CFlash PPMJTAGFlashToggle2NANDLINGDDR3MIPI CSIGDDR4MIPI DSIGDDR5MIPI M-PHY LBA NANDMIPI SLIMbus LPDDR2,3MIPI UniPro LRDIMMMIPI DigRF MMC 4.4OCPOne NANDPCI Express QDR SRAPCISD CardPLBSDIOSASSDRAMSATASRAMSerial Rapid IO SRAM cellularUSBToggle NANDUSB SuperSpeed Wide I/O SDRAMPlus othermemory types

<strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong>Simulator Support<strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong> products supportlogic simulators from all the major electronicdesign automation (EDA) providers.This ensures that customers can makemaximum use of their EDA investmentwhile performing consistent, high-qualityverification of standard interfaces.AXI4LiteStreamMIPIDigRFMIPIUniProMIPIM-PHYONFIEthernetJEDECAllianceAMBAHDMIOCP.orgMIPIAlliance USB.org SATA-IOPCI-SIGMIPISLIMbusPCIeGen3Super-SpeedUSBEthernet40G/100GEEEOCP 3.0 SATA 6G HDMI1.4DDR4LRDIMMFlashONFi 3.0Common Testbench InterfaceAll the <strong>VIP</strong> and memory models provide acommon testbench interface that reducesthe learning curve for verification teamsand simplifies the maintenance of complextest environments. For advancedSystemVerilog users, the <strong>VIP</strong> supports theindustry-standard UVM. Integration examplesare provided to ensure quick bring-uptime in SystemVerilog testbenches andreduced time-to-first-test.Emerging Protocol Leadership<strong>Cadence</strong> invests heavily in early support foremerging protocols, often providing <strong>VIP</strong>well before the new protocol specificationsreach the 1.0 release level. This investmenttakes the form of active participation inprotocol committees and working groupsand close collaboration with leading-edgecustomers. By providing early deliveryof <strong>VIP</strong>, <strong>Cadence</strong> is helping the industryto deliver game-changing products builtaround these new protocols.CMSEnabling First-to-Market Support of Emerging StandardsThe CMS provides a protocol-specific,metric-driven verification environmentthat includes:• Executable verification plan mapped tothe protocol specification• Library of constrained random tests toisolate design-under-test (DUT) cornercasesSupport Across EDAFigure 1: <strong>Cadence</strong> supports the rapid adoption of emerging protocols with early introduction ofnew <strong>VIP</strong>• Integrated coverage model to gradeverification completeness• Compliance checks and metrics toidentify DUT verification gapsProtocol compliance starts with theVerification Plan (vPlan). All verificationobjectives are captured in the vPlan andcorrelated to the protocol specification ona paragraph-by-paragraph basis. A libraryof constrained-random test sequencesVerifying Protocol ComplianceThe <strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong> offers twosolutions for advanced compliance verification—theCompliance ManagementSystem (CMS), and PureSuite.CMS provides parameterized test scenariosfor exploring the coverage space ina constrained-random simulation environment.Users set constraints to guide thegeneration of random test sequences toexplore areas of interest. Tight correlationbetween functional coverage results andthe protocol specification make it easyto interpret results and identify coverageholes.PureSuite provides an extensive library ofdirected compliance tests that are easy toimplement. The quick bring-up reducestime-to-first-test and the large test suitesprovide extensive compliance testing.Figure 2: CMS example showing AMBA AXI vPlan with coverage resulting from multiplesimulation runswww.cadence.com 2

<strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong>then stimulates the DUT with multipleparameter combinations for each coveragepoint of interest.Results from multiple simulation runs areintegrated and graphically displayed in thevPlan window. Cumulative coverage vs.plan is displayed and any coverage gapsare clearly identified. The verification engineerthen adjusts the test-generation constraintsto focus additional test sequenceson the coverage points of interest.Project management is facilitated throughvarious reports and charts, which measureprogress vs. plan. Early warning isthus provided for schedule deviations andresource limitations.PureSuiteEach PureSuite test is designed to coverspecific compliance checklist items, andeach test includes a detailed descriptionof purpose, assumptions, scenario, andexpected results. Tests are driven from the<strong>VIP</strong> across the protocol interface towardthe design under test, or can be initiatedfrom the application interface of thedesign. Capabilities include:• Thousands of pre-built tests forexercising specific functionality andcorner cases• Matched to the protocol’s compliancechecklist• Error recovery testing• All protocol layers and key statemachines coveredIncisive Assertion-Based <strong>VIP</strong>DUTI/FWhiteboxAssertionsI/F“We brought up the CMS compliance test suite in ourverification environment in just a day. Our team wasimpressed with the rapid results. We identified anumber of failures right away and we’re now workingto dramatically expand our regression runs totake full advantage of the CMS.”– Mike Bartley, Founder and CEO, TVS• Configurable based on DUT implementationand target device selection• Context-sensitive test selection• Specification and test coveragegeneration• Cumulative coverage reportingScalable Verification Solution<strong>Cadence</strong> provides users with a scalable<strong>VIP</strong> solution. Many <strong>VIP</strong> <strong>Catalog</strong> productsnot only support verification using popularlogic simulators, but also support acceleratedverification using the Palladiumplatform. This enables users to tradeoffverification functionality for speed as theyprogress from block to chip to systemlevelverification. In addition, <strong>Cadence</strong>provides assertion-based <strong>VIP</strong> for use with<strong>Cadence</strong> formal verification engines.Assertion-based <strong>VIP</strong> is particularly usefulfor design engineers since no stimulus isrequired.Interface ConstraintsInterface AssertionsFunctionalAssertionsFigure 3: Assertion-based <strong>VIP</strong> provides constraints and assertions to support formal analysisI/FI/FAssertion-Based <strong>VIP</strong>Assertion suites are provided for selectedprotocols. Typically consisting of 100 to200 protocol checks, these suites providea convenient mechanism for design engineersto participate in the verification oftheir modules. Using formal analysis toolssuch as <strong>Cadence</strong> Incisive ® Formal Verifier,modules may be verified while the designis still in process without requiring testbenchcreation.Formal VerificationFormal analysis uses properties todefine the desired behavior of a designwithin the design’s environment.There are two types of properties:• Assertions: Properties thatexpress the desired behavior of adesign under verification• Constraints: Properties thatexpress the behavior of theenvironmentThe assertion-based <strong>VIP</strong> includeshundreds of properties to formallyverify compliance to specifications.The properties are fully validated.Engineers can connect themdirectly to their design withoutconcern for false negative results.Since no stimulus or testbench isrequired, design engineers can initiatethe verification process before handingoff the design to the verification team.<strong>Cadence</strong> supports “pure formal”analysis with <strong>Cadence</strong> Incisive FormalVerifier, and integrated formal anddynamic simulation technologies in<strong>Cadence</strong> Incisive Enterprise VerifierXL. Both tools leverage the familiarSimVision GUI. This ensures ease ofuse when moving between simulationand formal verification.www.cadence.com 3

<strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong>Accelerated <strong>VIP</strong>To provide users high-end verificationperformance, many <strong>VIP</strong> <strong>Catalog</strong> productssupport accelerated verification using thePalladium platform. This enables usersto tradeoff verification functionality forspeed as they progress from block to chipto system-level verification.<strong>Cadence</strong> Accelerated <strong>VIP</strong> supports threedifferent use modes. These are transactionbasedC acceleration, transaction-basedUVM acceleration, and signal-based UVMacceleration. The C acceleration modeprovides the absolute highest performanceand throughput for system-level verification.The UVM acceleration modes enablereuse of the simulation testbench and ahigher degree of verification capability.This allows users to tradeoff performanceand verification capability to meet theirneeds at each stage in the design process.Advantages of <strong>Cadence</strong>Accelerated <strong>VIP</strong>• Easy to control tradeoff betweenperformance and verification capability• C acceleration mode for maximumperformance and throughput• UVM acceleration mode for maximumtestbench reuse• Verifies protocol compliance duringsimulation and accelerationFlexible Packaging<strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong> provides flexibility inproduct licensing to meet a wide range ofneeds. All <strong>VIP</strong> are available as individuala-la-carte licenses for dedicated protocolverification. The <strong>VIP</strong> and memory modelsare also available in portfolios to provide acost-effective solution for customers verifyingSoCs containing multiple protocolsor developing a range of projects whoseprotocol requirements vary over time.<strong>Cadence</strong> Services and Support• More information regarding<strong>Cadence</strong> <strong>VIP</strong> <strong>Catalog</strong> is available at:http://www.cadence.com/products/fv/ verification_ip• Hands-on demos of <strong>Cadence</strong>Verification IP are available at theXuropa online community:www.xuropa.com/cadenceIP• <strong>Cadence</strong> application engineers cananswer your technical questions bytelephone, email, or Internet—they canalso provide technical assistance andcustom training• <strong>Cadence</strong> Online Support gives you 24x7online access to a knowledgebase ofthe latest solutions, technical documentation,software downloads, and moreModest Verification Speed HighAccelerated <strong>VIP</strong>High Verification Functionality ModestSystemFigure 4: Accelerated <strong>VIP</strong> enables users to control tradeoffs between verification capability andperformanceUse ModelUser InterfacePerformanceEnvironmentReuseVerificationFunctionalityCompliance ManagementSystem (CMS)Signal-BasedAccelerationUVMModestHighHigh(Protocol Verification)UVM User InterfaceComplete ProtocolFunctional CoverageConstrained RandomTest GenerationComplete ProtocolCheckingTestbench BFMSignal InterfaceRTL DUTIES or PalladiumFigure 5: Three verification IP acceleration use modesUVMMediumHighMedium-HighUVM User InterfaceStreamlinedFunctional CoverageStreamlinedTest GenerationStreamlinedCheckingTransaction InterfaceSynthesizable BFMRTL DUTPalladiumTransaction-BasedAccelerationCHighModestModest(System DataflowVerification)C User InterfaceTransaction InterfaceSynthesizable BFMRTL DUTPalladium<strong>Cadence</strong> is transforming the global electronics industry through a vision called EDA360.With an application-driven approach to design, our software, hardware, IP, and services helpcustomers realize silicon, SoCs, and complete systems efficiently and profitably. www.cadence.com© 2011 <strong>Cadence</strong> Design Systems, Inc. All rights reserved. <strong>Cadence</strong> and the <strong>Cadence</strong> logo are registered trademarks of <strong>Cadence</strong> Design Systems, Inc.All others are properties of their respective holders. ARM and AMBA are trademarks of ARM Holdings Ltd. 21969D4 06/11 PC/IW/PDF