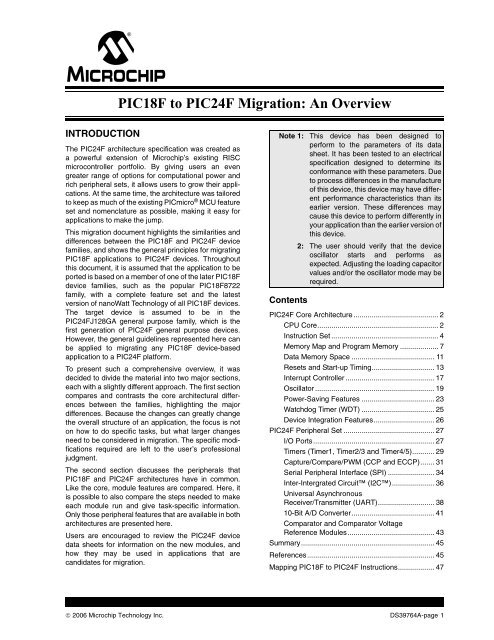

PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>PIC18F</strong> <strong>to</strong> <strong>PIC24F</strong> <strong>Migration</strong>: <strong>An</strong> <strong>Overview</strong>INTRODUCTIONThe <strong>PIC24F</strong> architecture specification was created asa powerful extension of <strong>Microchip</strong>’s existing RISCmicrocontroller portfolio. By giving users an evengreater range of options for computational power andrich peripheral sets, it allows users <strong>to</strong> grow their applications.At the same time, the architecture was tailored<strong>to</strong> keep as much of the existing PICmicro ® MCU featureset and nomenclature as possible, making it easy forapplications <strong>to</strong> make the jump.This migration document highlights the similarities anddifferences between the <strong>PIC18F</strong> and <strong>PIC24F</strong> devicefamilies, and shows the general principles for migrating<strong>PIC18F</strong> applications <strong>to</strong> <strong>PIC24F</strong> devices. Throughoutthis document, it is assumed that the application <strong>to</strong> beported is based on a member of one of the later <strong>PIC18F</strong>device families, such as the popular <strong>PIC18F</strong>8722family, with a complete feature set and the latestversion of nanoWatt Technology of all <strong>PIC18F</strong> devices.The target device is assumed <strong>to</strong> be in the<strong>PIC24F</strong>J128GA general purpose family, which is thefirst generation of <strong>PIC24F</strong> general purpose devices.However, the general guidelines represented here canbe applied <strong>to</strong> migrating any <strong>PIC18F</strong> device-basedapplication <strong>to</strong> a <strong>PIC24F</strong> platform.To present such a comprehensive overview, it wasdecided <strong>to</strong> divide the material in<strong>to</strong> two major sections,each with a slightly different approach. The first sectioncompares and contrasts the core architectural differencesbetween the families, highlighting the majordifferences. Because the changes can greatly changethe overall structure of an application, the focus is no<strong>to</strong>n how <strong>to</strong> do specific tasks, but what larger changesneed <strong>to</strong> be considered in migration. The specific modificationsrequired are left <strong>to</strong> the user’s professionaljudgment.The second section discusses the peripherals that<strong>PIC18F</strong> and <strong>PIC24F</strong> architectures have in common.Like the core, module features are compared. Here, itis possible <strong>to</strong> also compare the steps needed <strong>to</strong> makeeach module run and give task-specific information.Only those peripheral features that are available in botharchitectures are presented here.Users are encouraged <strong>to</strong> review the <strong>PIC24F</strong> devicedata sheets for information on the new modules, andhow they may be used in applications that arecandidates for migration.Note 1: This device has been designed <strong>to</strong>perform <strong>to</strong> the parameters of its datasheet. It has been tested <strong>to</strong> an electricalspecification designed <strong>to</strong> determine itsconformance with these parameters. Due<strong>to</strong> process differences in the manufactureof this device, this device may have differentperformance characteristics than itsearlier version. These differences maycause this device <strong>to</strong> perform differently inyour application than the earlier version ofthis device.2: The user should verify that the deviceoscilla<strong>to</strong>r starts and performs asexpected. Adjusting the loading capaci<strong>to</strong>rvalues and/or the oscilla<strong>to</strong>r mode may berequired.Contents<strong>PIC24F</strong> Core Architecture .......................................... 2CPU Core............................................................ 2Instruction Set ..................................................... 4Memory Map and Program Memory ................... 7Data Memory Space ......................................... 11Resets and Start-up Timing............................... 13Interrupt Controller ............................................ 17Oscilla<strong>to</strong>r ........................................................... 19Power-Saving Features .................................... 23Watchdog Timer (WDT) .................................... 25Device Integration Features.............................. 26<strong>PIC24F</strong> Peripheral Set ............................................. 27I/O Ports............................................................ 27Timers (Timer1, Timer2/3 and Timer4/5)........... 29Capture/Compare/PWM (CCP and ECCP)....... 31Serial Peripheral Interface (SPI) ....................... 34Inter-Intergrated Circuit (I2C)..................... 36Universal AsynchronousReceiver/Transmitter (UART)............................ 3810-Bit A/D Converter......................................... 41Compara<strong>to</strong>r and Compara<strong>to</strong>r VoltageReference Modules........................................... 43Summary.................................................................. 45References............................................................... 45Mapping <strong>PIC18F</strong> <strong>to</strong> <strong>PIC24F</strong> Instructions.................. 47© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 1

<strong>PIC24F</strong> CORE ARCHITECTURECPU CoreAside from its 16-bit data size, the <strong>PIC24F</strong> architectureis significantly different from the <strong>PIC18F</strong> architecture.The instruction word size, instruction clocking scheme,stack implementation and core registers are verydifferent from <strong>PIC18F</strong> implementations. Other hardwarefeatures have been added <strong>to</strong> enhance processingperformance. Changes are summarized in Table 1.TABLE 1:COMPARISON OF <strong>PIC18F</strong> AND <strong>PIC24F</strong> CPU CORE FEATURESFeature <strong>PIC18F</strong> <strong>PIC24F</strong>Instruction Size 16 bits 24 bitsInstruction Clocking TCY = FOSC/4 TCY = FOSC/2Working Registers 1 (W, WREG) 16 (W0-W15)Status Registers One (STATUS) Two (STATUS and CORCON)Stack Hardware, 31 levels SoftwareHardware Multiplier 8 x 8 17 x 17Hardware Divider No Hardware assisted division using DIV and REPEATBit Shifting/Rotation Single bit, left or right, rotation only Barrel shifting up <strong>to</strong> 15 bits, left or right, shift or rotateProgram Space Visibility(PSV)NoYesINSTRUCTION SIZEAll <strong>PIC18F</strong> devices use a 16-bit (single-word) instruction.<strong>PIC24F</strong> devices use a 24-bit instruction. A moredetailed discussion on instructions is presented in the“Instruction Set” section.INSTRUCTION CLOCKINGPICmicro microcontrollers execute instructions at a ratethat is a simple fraction of the clock speed, designatedas TCY. For the most part, <strong>PIC18F</strong> and <strong>PIC24F</strong> devicesperform most instructions with a fetch step and anexecution step of 1 TCY each. For <strong>PIC18F</strong> devices, eachTCY interval represents 4 clock cycles, with the PC beingincremented on falling edges. In contrast, the TCY for<strong>PIC24F</strong> devices is 2 clock cycles, with the PC beingincremented on leading clock edges. The differences ininstruction pipelining are shown in Figure 1. Thisdifference in instruction execution is one of the biggestdifferences between the two architectures, and needs <strong>to</strong>be taken in<strong>to</strong> consideration for any peripherals that usethe instruction clock speed as a base for their timing.FIGURE 1:COMPARISON OF <strong>PIC18F</strong> AND <strong>PIC24F</strong> INSTRUCTION EXECUTION PIPELINESDevice Clock<strong>PIC18F</strong> Program CounterPCPC + 2PC + 4<strong>PIC18F</strong> Execution PipelineExecute INST (PC – 2)Fetch INST (PC)Execute INST (PC)Fetch INST (PC + 2)Execute INST (PC + 2)Fetch INST (PC + 4)<strong>PIC24F</strong> Program Counter PC – 2PC PC + 2 PC + 4 PC + 6 PC + 8Fetch PC – 2 Execute PC – 2Fetch PC<strong>PIC24F</strong> Execution PipelineExecute PCFetch PC + 2 Execute PC + 2Fetch PC + 4 Execute PC + 4Fetch PC + 6 Execute PC + 6Fetch PC + 8DS39764A-page 2© 2006 <strong>Microchip</strong> Technology Inc.

W REGISTERSAll <strong>PIC18F</strong> devices have a single working register,known as W (sometimes, WREG). W is used as anoperand in almost all instructions, and is either thesource or destination for all instructions.The <strong>PIC24F</strong> architecture increases the number ofworking registers <strong>to</strong> 16, named W0 through W15. Mostinstructions allow for the selection of any one of theseas source and/or destination for the operation, althoughseveral instructions only allow the use of WREG (W0).Several of the registers have special functions. W0 andW1 are the working registers for the hardware-assisteddivider, and are required during divide (DIV) instructions.W2 and W3 are used by the MUL instruction asresult registers. W14 and W15 are used for a FramePointer and Stack Pointer, respectively.STATUS REGISTERS<strong>PIC18F</strong> devices have one ALU status register, namedSTATUS. It contains the normal flag bits for binarydigital math operations: Carry, Digit Carry, Zero state,Negative state and Overflow. All flags are writable aswell as readable.<strong>PIC24F</strong> devices use two status registers, which providethese ALU flags as well as CPU control bits. TheSTATUS register contains the standard ALU flagsalready listed; it also contains the RA flag <strong>to</strong> indicate anactive Repeat loop and the IPL2:IPL0 bits <strong>to</strong> set theCPU interrupt priority level.In addition <strong>to</strong> STATUS, <strong>PIC24F</strong> devices also have theCORCON register. It contains the IPL3 bit, whicheffectively enables or disables peripheral interrupts andthe PSV bit, which enables the Program SpaceVisibility feature (see “Data Memory Space” onpage 11 for more information).STACK<strong>PIC18F</strong> devices implement the program counter stackin hardware. The stack has a <strong>to</strong>tal of 32 levels, with onlythe <strong>to</strong>p layer being accessible <strong>to</strong> software. Stackpushes and pops are executed as instructions. <strong>An</strong>optional, non-maskable hardware trap (Reset) can beenabled for stack overflow and underflow events.In contrast, <strong>PIC24F</strong> devices implement a softwarestack in data RAM. The stack starts at RAM address0800h and grows <strong>to</strong>wards higher addresses. W15serves as the Stack Pointer and W14 is used as aFrame Pointer for higher level language applications.The upper limit of the stack is defined in software usingthe SPLIM register. Stack Pointer underflow andoverflow traps are generated when the Stack Pointer isdecremented below 0800h, or above the limit set bySPLIM.MULTIPLIERBoth <strong>PIC18F</strong> and <strong>PIC24F</strong> devices include a dedicatedhardware multiplier in their ALUs. The <strong>PIC18F</strong> multiplieris an 8 x 8 unit, capable of supporting signed,unsigned and mixed-sign operations. The <strong>PIC24F</strong>multiplier is a 17 x 17 unit and can also support signed,unsigned and mixed-signed operations. <strong>PIC18F</strong> multiplierscan perform 8-bit unsigned operations in a singleinstruction cycle, while <strong>PIC24F</strong> multipliers can performa 16-bit by 16-bit signed or mixed operation in a singlecycle.DIVIDER<strong>PIC18F</strong> devices do not provide any hardware supportfor division. Typical divide operations (signed 16/16 or16/8) performed, using the standard <strong>PIC18F</strong> mathlibrary, can take up <strong>to</strong> 38 instruction cycles <strong>to</strong> execute.<strong>PIC24F</strong> devices do not have a hardware divider per se.Instead, the <strong>PIC24F</strong> ALU is configured in hardware <strong>to</strong>support a divide instruction, DIV. Together with theREPEAT control instruction, DIV allows the ALU <strong>to</strong>au<strong>to</strong>matically execute the iterative division process asa simple sequence instead of a long algorithm. DIVsupports several forms of 32/16 and 16/16 divides,including fixed-point and fractional, and performsexecutions in 19 instruction cycles.BIT SHIFTS AND ROTATESThe <strong>PIC18F</strong> ALU is capable of performing single bitposition rotations, with or without carry, in either direction.<strong>An</strong>y byte operation that requires rotations of morethan one position will require an equal number ofinstruction cycles <strong>to</strong> perform the operation. Word lengthoperations are potentially longer and more complex, asbits need <strong>to</strong> be carried from one byte of data <strong>to</strong> another.The <strong>PIC24F</strong> ALU is equipped with a barrel shifter thatallows data <strong>to</strong> be either rotated or shifted (without wraparound),with or without carry, in either direction. Thispermits shifts of multiple bit positions in a single instructioncycle. Data can be rotated either as bytes for up <strong>to</strong>7 bits at a time, or as words for up <strong>to</strong> 15 bits at a time.© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 3

Instruction SetThe <strong>PIC24F</strong> instruction set architecture represents aconsiderable extension of its <strong>PIC18F</strong> predecessor.While barely larger in terms of base instructions, itmakes substitutions of selected instructions <strong>to</strong>enhance the performance, while expanding the scopeof addressing modes and data type operations.Through all of this, the <strong>PIC24F</strong> instruction set maintainsthe highly orthogonal structure of previous PICmicroarchitectures.The main differences between the <strong>PIC18F</strong> and <strong>PIC24F</strong>instruction sets are presented in Table 2.TABLE 2:COMPARISON OF MAJOR INSTRUCTION SET FEATURESFeature <strong>PIC18F</strong> <strong>PIC24F</strong>Instruction Size 16 bits 24 bitsBase Instructions 75 76Supported Data Types Byte Byte, Word, Double WordOperand Support Up <strong>to</strong> binary (b = a + b) Up <strong>to</strong> trinary (a + b = c)Addressing Modes Direct, Indirect (5) Direct, Indirect (6)Indirect Addressing Type Uses FSR Pointer register sets; limit of3 pointersUses any of the W registers as pointers withinstruction-based manipulation; limit of 16Data Space AddressingShort literal, limited <strong>to</strong> a single bank a<strong>to</strong>ne time; full literal on few instructionsShort literal for entire Near Data Space;indirect address for entire spaceCHANGES FROM <strong>PIC18F</strong> INSTRUCTION SETThe <strong>PIC24F</strong> instruction set implements severalfeatures that enhance performance for math operations,and extend the ability <strong>to</strong> handle high-levellanguages with more complex stack and pointerrequirements. These are summarized in Table 3.In addition, several <strong>PIC18F</strong> instructions do not have anexact single instruction equivalent in the <strong>PIC24F</strong> architecture.Most of these instructions have either single orpairs of <strong>PIC24F</strong> instructions that have similar effect, butbecause of differences in the STATUS register, resultsare not exactly equivalent. They are:• CPFSEQ• INFSNZ• CPFSGT• MOVSF• CPFSLT• MOVSS• DCFSNZ• PUSHL• DECFSZ• SUBULNK• INCFSZ• TSTFSZ• MOVFF (all modes except indirect <strong>to</strong> indirect)• SWAPF (all modes except with WREG)Even with these changes, most <strong>PIC18F</strong> assemblerinstructions have a single-cycle equivalent in the<strong>PIC24F</strong> assembler. A comprehensive list is providedin Appendix A: “Mapping <strong>PIC18F</strong> <strong>to</strong> <strong>PIC24F</strong>Instructions”.TABLE 3:NEW OR SIGNIFICANTLY MODIFIED <strong>PIC24F</strong> INSTRUCTIONS<strong>PIC24F</strong> InstructionDescriptionDIV Divide two numbers (signed or unsigned, 16/16 or 32/16)LNK and UNLKLink or unlink Frame Pointer (W14)LSR and ASRLogical or arithmetic shift right by 1 <strong>to</strong> 16 bits, by either a literal or variable valueMUL.SS, MUL.SU, Specific instructions for multiplying signed and unsigned numbersMUL.USPUSH and POPBoth instructions now include source or destination arguments, allowing the stack <strong>to</strong>s<strong>to</strong>re values other then the current PCREPEATRepeat the next instruction a specified number of timesSLShift left by 1 <strong>to</strong> 16 bits by either a literal or variable valueDS39764A-page 4© 2006 <strong>Microchip</strong> Technology Inc.

SUPPORTED DATA TYPESAside from bit-oriented instructions, <strong>PIC18F</strong>instructions operate exclusively on single byte data.<strong>An</strong>y data that is longer than a single byte is handled byconcatenating bytes in the proper order.As 16-bit devices, <strong>PIC24F</strong> instructions are designed <strong>to</strong>handle data in terms of 16-bit words. In addition, mostinstructions are capable of handling single byte anddouble word (32-bit) data objects. Invoking this featureis generally done by using the suffix “.b” (for bytes) or“.d” (for double words) after the instruction mnemonic.Data alignment within the memory space is au<strong>to</strong>maticallyadjusted and maintained according <strong>to</strong> the datatype selected.OPERAND SUPPORTThe <strong>PIC18F</strong> instruction set supports both unary andbinary operations. That is <strong>to</strong> say, an instruction canfunction with a single argument operating on the contentsof one register (e.g., increment the WREG), orwith two arguments s<strong>to</strong>ring the results in one of the tworegisters (e.g., adding the contents of a register <strong>to</strong>WREG and s<strong>to</strong>ring the sum in WREG).The <strong>PIC24F</strong> instruction set also supports trinaryoperations; that is, an operation can have three arguments,specifying not only two operands but also anindependent address for the result. Trinary operationsare supported for most arithmetic and logic instructions.ADDRESSING MODESThe biggest difference between the <strong>PIC18F</strong> and<strong>PIC24F</strong> instruction sets is how the instructions specifyaddresses in the data memory space. While the methodsare equivalent, the <strong>PIC24F</strong> version allows moreoptions for more of its instructions.Direct AddressingWhile <strong>PIC18F</strong> instructions can directly address anyregister in the data space, very few specify a fulladdress as part of the instruction. Instead, most use an8-bit literal value <strong>to</strong> specify an address within one of16 banks of 256 bytes within the space. The bank inquestion is separately selected by the Bank SelectRegister (BSR).<strong>PIC24F</strong> instructions are designed <strong>to</strong> be able <strong>to</strong> literallyaddress any register within the lowest 8 Kbytes of thedata space (also known as the Near Data Space). Thisallows immediate access <strong>to</strong> all SFRs. Implementedmemory areas above the <strong>to</strong>p of the Near Data Spaceare accessible by indirect addressing, as describedbelow.Indirect Addressing<strong>PIC18F</strong> instructions perform indirect addressingthrough pointers and virtual registers. Three 12-bitpointers (FSR0 through FSR2) are loaded withappropriate values; then, one of five virtual registersassociated with that pointer is used as an argument foran instruction, either as an address or an offset for anaddress. Depending on which of the registers is used,the value of the pointer can also be au<strong>to</strong>matically incrementedor decremented. Only these three pointers andtheir associated registers can be used for indirectaddressing.In contrast, <strong>PIC24F</strong> architecture increases the numberof options for the addressing mode. <strong>An</strong>y one of the Wregisters can be used as a pointer for indirect addressing.Instead of using a virtual register name <strong>to</strong> determinethe pointer and its operation, the MPLAB ® IDEassembler language uses specific syntax conventions<strong>to</strong> indicate when a W register is being used as a pointeror offset, and what increment or decrement operation is<strong>to</strong> be done <strong>to</strong> the register. The <strong>PIC24F</strong> Instruction SetArchitecture (ISA) also offers a pre-decrement optionnot available with <strong>PIC18F</strong>. <strong>An</strong> additional feature of the<strong>PIC24F</strong> increment/decrement options is how they workwith the data type specified by the instruction. If theinstruction is executed as a byte type instruction, theregister will be incremented or decremented by one.This aligns the pointer <strong>to</strong> the next byte in memory whichis not always the next memory address. Word-orientedinstructions will increment or decrement the register bytwo and maintain proper word alignment.The differences between architectures in indirectaddressing modes and syntax are summarized inTable 4. A comparison of how <strong>to</strong> use these addressingmodes is shown in Example 1.TABLE 4:Indirect AddressingModeINDIRECT ADDRESSING IN <strong>PIC18F</strong> AND <strong>PIC24F</strong> INSTRUCTION SETS<strong>PIC18F</strong> VirtualRegister Operand<strong>PIC24F</strong> EquivalentSyntaxAfter ByteInstructionWn (or FSR)After WordInstructionNo Modification INDFx [Wn] Wn = Wn Wn = WnPre-Increment PREINCx [++Wn] Wn = Wn + 1 Wn = Wn + 2Pre-Decrement N/A [--Wn] Wn = Wn – 1 Wn = Wn – 2Post-Increment POSTINCx [Wn++] Wn = Wn + 1 Wn = Wn + 2Post-Decrement POSTDECx [Wn--] Wn = Wn – 1 Wn = Wn – 2Register Offset PLUSWx [Wn + Wb] Wn = Wn Wn = Wn© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 5

EXAMPLE 1: COMPARISON OF INDIRECT ADDRESSING TECHNIQUESTypical <strong>PIC18F</strong> Code Sequence:LoopSetup MOVLW 0x10, LoopCount ;set up loop counterLFSR 0, myArray0 ;set up pointer 0LFSR 1, myArray1 ;set up pointer 1CopyLoop MOVFF POSTINC0, POSTINC1 ;copy myArray1 <strong>to</strong> myArray0DECFSZ LoopCount, F ;decrement loop counterBRA CopyLoop ;loopEquivalent <strong>PIC24F</strong> Code Sequence:LoopSetup MOV #myArray0, W0 ;set up pointer 0MOV #myArray1, W1 ;set up pointer 1CopyLoop REPEAT #15 ;loop 16 timesMOV [W1++], [W0++] ;copy array1 <strong>to</strong> arrayRAW DependenciesThe increased flexibility in addressing modes creates afew situations where Read-After-Write (or RAW)dependencies may be created. RAW dependenciesexist when a variable needed for an instruction that isbeing fetched stage has not been written back <strong>to</strong> theregister yet. These occur only in select situations,generally when a register used as a destination for oneinstruction is also an argument in an immediatelyfollowing instruction, and are listed in Table 5. The<strong>PIC24F</strong> CPU core includes “look ahead” detection forthese RAW hazards, and introduces one or more stall(NOP) cycles between instructions <strong>to</strong> avoid executionerrors.TABLE 5:SUMMARY OF READ-AFTER-WRITE DEPENDENCY RULESDestinationAddressing ModeUsing WnSourceAddressing ModeUsing WnRequired Stall(CPU cycles added<strong>to</strong> instruction time)Examples(Wn = W2)Direct Direct None ADD.w W0, W1, W2MOV.w W2, W3Indirect Direct None ADD.w W0, W1, [W2]MOV.w W2, W3Indirect Indirect None ADD.w W0, W1, [W2]MOV.w [W2], W3IndirectIndirect withpre/post-modificationIndirect withpre/post-modificationNoneADD.w W0, W1, [W2]MOV.w [W2++], W3Direct None ADD.w W0, W1, [W2++]MOV.w W2, W3Direct Indirect 1 ADD.w W0, W1, W2MOV.w [W2], W3DirectIndirect withpre/post-modification1 ADD.w W0, W1, W2MOV.w [W2++], W3Indirect Indirect 1 ADD.w W0, W1, [W2]MOV.w [W2], W3; W2=04h (mapped W2)IndirectIndirect withpre/post-modificationIndirect withpre/post-modificationIndirect withpre/post-modification1 ADD.w W0, W1, [W2]MOV.w [W2++], W3; W2=04h (mapped W2)Indirect 1 ADD.w W0, W1, [W2++]MOV.w [W2], W3Indirect withpre/post-modification1 ADD.w W0, W1, [W2++]MOV.w [W2++], W3DS39764A-page 6© 2006 <strong>Microchip</strong> Technology Inc.

Memory Map and Program MemoryBoth <strong>PIC18F</strong> and <strong>PIC24F</strong> architectures use the samegeneral schema for their program memory spaces.Aside from the self-evident differences in width,<strong>PIC24F</strong> devices also incorporate a larger addressingrange and enhanced visibility features in data space.The organization of the space and the location ofnon-program memory features also differ somewhat,and must be considered when porting an application.The key differences between the memory organizationof <strong>PIC18F</strong> and <strong>PIC24F</strong> devices are presented inTable 6.TABLE 6:COMPARISON OF <strong>PIC18F</strong> AND <strong>PIC24F</strong> PROGRAM MEMORY ARCHITECTURESFeature <strong>PIC18F</strong> <strong>PIC24F</strong>Organization 16-bit, byte addressable 24-bit, word addressableTotal Addressable Range 4 Mbytes (22-bit magnitude) 16 Mbytes (24-bit magnitude)Maximum Available User Program Space 2 Mbytes (FFFFFh) 8 Mbytes (7FFFFFh)(upper boundary address)Boot Block Support Most devices NoInterrupt/Reset/Trap Vec<strong>to</strong>rs 00h, 08h, 18h 00h <strong>to</strong> 1FFhConfiguration Word Locations 300000h <strong>to</strong> 30000Fh Last 2 implemented locations inprogram memoryDevice ID Locations 3FFFFE and 3FFFFFh FF0000h and FF0002hORGANIZATIONThe <strong>PIC18F</strong> program space is organized as 16-bitwords, but is addressable in terms of bytes. Thismeans that the upper or lower byte of any word can beindividually addressed by a pointer. To maintain wordalignment for code execution, the memory space isaligned on the Least Significant Byte (LSB) of eachword, and the program counter increments by 2 duringnormal execution.The <strong>PIC24F</strong> program space has a different, but parallelstructure. It is physically organized as 24 bits wide, butis addressed as 16-bit words. Thus, an instruction isconsidered <strong>to</strong> be two words, not 3 bytes. Each wordcan be individually addressed with even addressesrepresenting the lower word of an instruction and oddaddresses the upper word. To maintain instructionalignment, the memory space is aligned on evenwords; the program counter increments by 2 duringnormal execution.Since a <strong>PIC24F</strong> instruction is three bytes wide, theMost Significant Byte of an instruction finds itself alonein the most significant word of the instruction as it iss<strong>to</strong>red in memory. To maintain word alignment whenreading from, or writing <strong>to</strong> program memory, a“phan<strong>to</strong>m byte” of 00h is added before the MSB <strong>to</strong> giveit the proper word length (Figure 2). The value reflectsthat this byte is not actually implemented in physicalprogram memory.Even with its word-aligned addressing, any single bytewithin the program space can be individually read orwritten. The <strong>PIC24F</strong> TBLRD and TBLWT commands areextended <strong>to</strong> allow an individual upper or lower byte ofany word <strong>to</strong> be accessed. Keep in mind that the upperbyte of any upper word (odd address) will always be00h, and cannot be written <strong>to</strong>, for reasons previouslydiscussed.FIGURE 2:<strong>PIC24F</strong> PROGRAM MEMORY ORGANIZATIONMSWAddressMost Significant WordLeast Significant WordPC Address(LSW Address)000001h000003h000005h000007h00000000000000000000000000000000231680000000h000002h000004h000006hProgram Memory‘Phan<strong>to</strong>m’ Byte(read as ‘0’)Instruction Width© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 7

ADDRESSABLE AND USER-AVAILABLE RANGEBoth architectures base the size of their program spaceentirely on the size of the program counter. <strong>PIC18F</strong>devices use a 22-bit program counter for a <strong>to</strong>taladdressable space of 4 Mbytes. <strong>PIC24F</strong> devices use a24-bit counter for a <strong>to</strong>tal range of 16 Mbytes.In addition, both architectures reserve the upper half ofthe addressable program space as “configurationspace”; this is largely unimplemented addresses, withseveral implemented areas for device configuration,identification and programming. Thus, the <strong>to</strong>tal maximumavailable space for program memory is 2 Mbytesfor <strong>PIC18F</strong> devices, and 8 Mbytes for <strong>PIC24F</strong> devices.It is worth noting that no device in either family entirelyimplements the full available range of program memoryspace.The program spaces for the two architectures areshown in comparison in Figure 3.FIGURE 3: COMPARISON OF <strong>PIC18F</strong> AND <strong>PIC24F</strong> PROGRAM MEMORY SPACES (1)<strong>PIC18F</strong> Family (2)<strong>PIC24F</strong> Family000000h000008h000018hReset Vec<strong>to</strong>rLow/High Interrupt Vec<strong>to</strong>rsGOTO InstructionReset AddressInterrupt Vec<strong>to</strong>r TableReservedAlternate Vec<strong>to</strong>r Table000000h000002h000004h0000FEh000100h000104h0001FEh000200hUser FlashProgram Memory(up <strong>to</strong> 128 Kbytes)Program Memory AreaUser FlashProgram Memory(up <strong>to</strong> 128K words)(Top of PM)Device Config Words(Top of PM)-4(Top of PM)Unimplemented(Read ‘0’s)Unimplemented(Read ‘0’s)1FFFFEh200000h7FFFFEh800000hReserved2FFFFFh300000h30000Fh300010hDevice ConfigurationRegistersConfiguration SpaceReservedReserved3FFFFEh3FFFFFhDEVID (2)DEVID (2)FEFFFEhFF0000hFFFFFFhNote 1: Memory areas are not shown <strong>to</strong> scale. Scales differ for <strong>PIC18F</strong> and <strong>PIC24F</strong> maps.2: Only the elements of program space common <strong>to</strong> all <strong>PIC18F</strong> devices are shown. Later features, such as BootBlocks and Flash Configuration Words (<strong>PIC18F</strong>XXJ Flash devices only) have been omitted for clarity.DS39764A-page 8© 2006 <strong>Microchip</strong> Technology Inc.

INTERRUPT/RESET/TRAP VECTORSIn <strong>PIC18F</strong> devices, three addresses at the bot<strong>to</strong>m ofprogram memory are reserved for hardware vec<strong>to</strong>rs.Application code for these devices places destinationaddresses for hardware Resets, high-level InterruptService Routines (ISRs) and low-level ISRs in 00h, 08hand 18h, respectively.In <strong>PIC24F</strong> devices, the reserved range is much larger:from 00h <strong>to</strong> 1FFh. Location 00h is still reserved for thehardware Reset vec<strong>to</strong>r. Addresses 06h through FFhare reserved for the main interrupt vec<strong>to</strong>r table, whichcontains 118 separate hardware address vec<strong>to</strong>rs(including 8 non-maskable hardware traps). Addresses100h through 1FFh contain an alternate interrupt vec<strong>to</strong>rtable, also of 118 hardware address vec<strong>to</strong>rs, that isreserved for use in Emulation mode.CONFIGURATION WORDS AND DEVICE IDSBoth <strong>PIC18F</strong> and <strong>PIC24F</strong> devices locate their fac<strong>to</strong>rydevice IDs in the configuration space above the programmemory area. <strong>PIC18F</strong> Configuration registers are alsolocated in configuration space, whereas <strong>PIC24F</strong> Configurationregisters are located in program memory.<strong>PIC18F</strong> devices locate their Configuration Words at300000h through 30000Fh, and device IDs at 3FFFFEhand 3FFFFFh. <strong>PIC24F</strong> devices locate their ConfigurationWords at the last two addresses in implementedprogram memory, and device IDs at FF0000h andFF0002h.BOOT BLOCK SUPPORTMany <strong>PIC18F</strong> devices allow users <strong>to</strong> reserve andindependently code-protect a small area at the base ofthe user program space (depending on the device,between 1 and 4K words) for an independentbootloader program.As of this writing, a similar feature is not implementedin <strong>PIC24F</strong> devices. This absence does not rule out theuse of bootloader programs; it only means that a dedicatedand separately protectable block of programmemory is not available.EXTERNAL MEMORY MAPPINGThe <strong>PIC18F</strong> architecture supports the use of externalmemory devices as program memory. This feature,known as the External Memory Interface (EMI), isactually implemented as part of the CPU core’s addressbus management system. The EMI allows the programaddress bus <strong>to</strong> address and retrieve data from off-chipdevices as if they were part of the 2 Mbyte, on-chip programspace. Multiple operating modes are implemented,such as using off-chip memory exclusively as programmemory. Because of the I/O requirements, the EMI isonly available on <strong>PIC18F</strong> devices with 80 or more pins.As of this writing, <strong>PIC24F</strong> devices do not offer thisfeature. Program size is limited <strong>to</strong> that of on-chipmemory.FLASH MEMORY OPERATIONMany <strong>PIC18F</strong> and <strong>PIC24F</strong> devices use selfprogrammableFlash technologies <strong>to</strong> implementprogram memory. The general schema of memoryoperations and how they are performed are verysimilar, such as:• the ability <strong>to</strong> self-program some or all of the Flashmemory during run time• the ability <strong>to</strong> program or reprogram a devicealready embedded in the application through a5-wire serial interface (In-Circuit SerialProgramming or ICSP), or during deviceoperation (Enhanced In-Circuit SerialProgramming or EICSP)• the use of erase and write blocks of defined sizes,and erase-before-write programming algorithms• the self-timed write process after filling a writebuffer block, which stalls CPU execution for oneor more TCYOnly those differences that may impact the migration ofan application are noted here.Register and Bit Nomenclature<strong>PIC18F</strong> and <strong>PIC24F</strong> devices all use a single controlregister and a single unlock register <strong>to</strong> control Flashoperations. Some register and bit names, as shown inTable 7, change between the architectures.TABLE 7:FLASH CONTROL REGISTERSAND BITS IN <strong>PIC18F</strong> AND<strong>PIC24F</strong> ARCHITECTURESFlash Register or BitDescription<strong>PIC18F</strong> <strong>PIC24F</strong>Flash Control Register EECON1 NVMCONFlash Key Register EECON2 NVMKEYEEPROM Data Register EEPGD —PM/EEPROM Destination CFGS —Select bitFlash Operation EnablebitFREE ERASEThe key Flash control bits (WR, WREN and WRERR)have the same names and functions in botharchitectures.© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 9

Flash AddressingIn <strong>PIC18F</strong> devices, the target address of Flash operationsis specified by a 22-bit Table Pointer register,TBLPTR, that is composed of 3 single byte SFRs(TBLPTRL, TBLPTRH and TBLPTRU). All table readand write instructions use this pointer <strong>to</strong> address theentire memory space; however, only table read operationsare allowed when the configuration space isaddressed (TBLPTR = 1).In <strong>PIC24F</strong> devices, the target address for Flashoperations is specified by two registers: the 8-bit TablePage register (TBLPAG) which specifies a 64 Kbytearea of the program memory space, and one of the Wregisters <strong>to</strong> specify an exact address within a designatedpage. The value of the two registers <strong>to</strong>getherforms the Effective Address or EA. As with <strong>PIC18F</strong>devices, only read operations are allowed when theconfiguration space is addressed (TBLPAG = 1).Data Size in Table OperationsTable operations in the <strong>PIC18F</strong> architecture are allbyte-oriented. All bytes in the memory space are individuallyaddressable, with the particular byte (high orlow) defined by an odd or even address argument.As already mentioned, table operations in the <strong>PIC24F</strong>architecture can be byte or word-oriented. In the latter,the specific byte (high or low) is defined by theinstruction mnemonic itself (TBLRDH/TBLRDL andTBLWTH/TBLWTL). The byte option can also be specified<strong>to</strong> specifically operate on either byte of any givenword. Keep in mind, of course, that operations on theupper byte of the upper word will either return 00h, orhave no effect, for reasons previously described.Reading Program Memory in Run Time<strong>PIC18F</strong> devices can retrieve data from the programspace using the table read command. Data is retrievedone byte at a time.<strong>PIC24F</strong> devices can also retrieve data with table reads,either one word or one byte at a time. In addition, theycan also use the PSV feature <strong>to</strong> map a 32 Kbyte blockof the program space in<strong>to</strong> the <strong>to</strong>p half of the data spaceon a read-only basis. This is further explained in the“Data Memory Space” section on page 11.DATA EEPROMMany <strong>PIC18F</strong> devices offer on-chip, nonvolatile datamemory for the s<strong>to</strong>rage of constant or slowly changingapplication data. These EEPROM areas are readableand writable, and are controlled by the same registersused <strong>to</strong> operate the Flash program memory.As of this writing, <strong>PIC24F</strong> devices do not incorporatedata EEPROMs in any devices. Users requiring a place<strong>to</strong> keep nonvolatile application data can use an unusedblock of program memory for this purpose. Data can beaccessed and modified using table read and writeoperations, and read using PSV mode.DS39764A-page 10© 2006 <strong>Microchip</strong> Technology Inc.

Data Memory SpaceThe <strong>PIC24F</strong> data memory space is substantiallydifferent than that found in <strong>PIC18F</strong> devices. The size,organization and method of access have all beenchanged. The key differences between the twoarchitectures are shown in Table 8.TABLE 8:COMPARISON OF MAJOR DATA MEMORY SPACE FEATURESFeature <strong>PIC18F</strong> <strong>PIC24F</strong>Addressing Range (size) 12 bits (4,096 byte maximum) 16 bits (65,536 byte maximum)SegmentationLinear range, banked addressing; linear Linear range, no segmentationaddressing for some instructionsSpecial Access Areas Access RAM (bot<strong>to</strong>m of lowest bank,Near Data Space (bot<strong>to</strong>m 8K)<strong>to</strong>p of highest bank)SFR Location Top half of highest bank Distributed throughout Near MemoryStackHardware, 32 levels deep, not mappedin memory spaceSoft stack starting at 0800h, user-configurableend of stackData Access Byte (direct or indirect) Double word, word or byte (all direct or indirect)Hardware PSV No Yes, in<strong>to</strong> <strong>to</strong>p half of data spaceADDRESS RANGE AND SEGMENTATIONAll <strong>PIC18F</strong> devices have a data memory space with a12-bit address range. In theory, the data space has alinear range and can be addressed directly by severalof the <strong>PIC18F</strong> instructions. For the most part, however,the data space functions as a segmented space. Sincemost <strong>PIC18F</strong> instructions can only contain the 8 lowerbits of a data address, the data space is effectivelydivided in<strong>to</strong> 16 banks of 256 bytes each. The exactmemory location is also determined by the Bank SelectRegister (BSR) which contains the upper 4 bits of theaddress. The entire range of the data space is4 Kbytes, of which some or all, may be implemented asdata RAM.In contrast, the <strong>PIC24F</strong> data space is implemented asa single linear range of addresses. Most instructionscan directly access any address within the first8 Kbytes of the range without the use of bank selection.The entire data space range is 64 Kbytes. Of this, onlythe first 32 Kbytes are implementable as data RAM; theupper 32 Kbytes are a virtual memory space that isused for PSV (see “Program Space Visibility (PSV)”on page 11).A comparison of the data space maps is shown inFigure 4.SFR LOCATIONSIn <strong>PIC18F</strong> architecture, all SFRs are located at the very<strong>to</strong>p of data memory, generally from addresses F60h <strong>to</strong>FFh, as a more or less contiguous block.In <strong>PIC24F</strong> architecture, SFRs reside in the lowest2 Kbytes of the memory space, from addresses 0000hthrough 07FFh.SPECIAL ACCESS AREASThe effective segmentation of the <strong>PIC18F</strong> data spacemakes it necessary for some way of accessing SFRsand critical application data quickly. This is done bycreating a virtual data space bank, known as theAccess RAM, which is composed of the lower half ofthe lowest bank and the upper half of the upper bank.This scheme makes certain that the SFR space isalways available, regardless of the contents of theBSR. Use of the Access RAM is included as an argumentin <strong>PIC18F</strong> assembly language and is hard-codedin the instruction’s opcode.In the <strong>PIC24F</strong> data space, the first 8 Kbytes of dataRAM between the addresses of 0000h and 1FFFh arereferred <strong>to</strong> as the Near Data Space. Addresses in thisspace, including all SFRs, are accessible directly fromall direct memory access instructions.PROGRAM SPACE VISIBILITY (PSV)Both <strong>PIC18F</strong> and <strong>PIC24F</strong> architectures allow for thedirect access of information s<strong>to</strong>red in the programmemory space as data. For <strong>PIC18F</strong>, data from programmemory is read in the data space by use of TBLRDcommands, with access being done on a word-by-wordbasis.For <strong>PIC24F</strong> devices, program memory is also madeavailable through hardware-enabled Program SpaceVisibility (PSV). When used, any 32 Kbyte segment ofthe program space may be mapped in<strong>to</strong> the upper32 Kbyte area of the data space on a read-only basis.PSV uses a hardware register, PSVPAG, <strong>to</strong> define whichpage of program memory will be mapped. The PSV iscontrolled in software by the PSV bit (CORCON).© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 11

FIGURE 4:COMPARISON OF <strong>PIC18F</strong> AND <strong>PIC24F</strong> DATA SPACE MAPS<strong>PIC18F</strong> Devices<strong>PIC24F</strong> Devices00hBank 0FFh00hBank 1FFh00hBank 2FFh00hBank 3FFh00hBank 4FFh00hBank 5FFh00hBank 6FFh00hBank 7FFh00hBank 8FFh00hBank 9FFh00hBank 10FFh00hBank 11FFh00hBank 12FFh00hBank 13FFh00hBank 14FFh00hBank 15FFhAccess RAMGPRGPRGPRGPRGPRGPRGPRGPRGPRGPRGPRGPRGPRGPRGPRGPRSFR000h05Fh060h0FFh100h1FFh200h2FFh300h3FFh400h4FFh500h5FFh600h6FFh700h7FFh800h8FFh900h9FFhA00hAFFhB00hBFFhC00hCFFhD00hDFFhE00hEFFhF00hF5FhF60hFFFhAccess BankAccess RAM LowAccess RAM High(SFRs)00h5Fh60hFFhNearDataSpaceSFR AreaData RAM Area(implementation varieswith device)PSV Space0000h07FFh0800h1FFFh2000h7FFFh8000hFFFFhBank determined by Bank Select Register (BSR)Note:GPR = General Purpose RAM. Memory spaces are shown at different relative scales.PROGRAM STACKAs discussed in the “CPU Core” on page 2, <strong>PIC18F</strong>devices use a hardware stack for program flowmanagement. The stack is not memory mapped andhas a fixed size of 32 levels.<strong>PIC24F</strong> architecture uses a stack implemented entirelyin mapped data space. The stack begins at 0800h inNear Data Memory, just outside of the SFR area, andgrows <strong>to</strong>wards higher memory addresses, using theW15 register as a dedicated pointer. The size of thestack is entirely user-defined with the SFR register,SPLIM, which sets the address for stack overflow traps.DATA ACCESSAs discussed in the “Instruction Set” section onpage 4, <strong>PIC18F</strong> architecture can only work with data interms of bytes. In contrast, the <strong>PIC24F</strong> data space,organized in 2-byte words, allows many instructions <strong>to</strong>work with data as bytes, words or double words(32 bytes). The data type is determined by theargument used with the instruction.DS39764A-page 12© 2006 <strong>Microchip</strong> Technology Inc.

Resets and Start-up TimingThe <strong>PIC24F</strong> device Reset system can be thought of asa superset of the <strong>PIC18F</strong> version. The same legacyResets are supported in either identical or functionallyequivalent methods:• Power-on Reset (POR)• Brown-out Reset (BOR)• External Master Clear Reset (MCLR)• Software Reset (RESET instruction)• Watchdog Timer (WDT) Reset• Stack Error (Overflow or Underflow)<strong>PIC24F</strong> devices enhance the system with Resets foradditional error states, along with enhanced reporting.The Reset states for SFRs and start-up timing fromResets also differs slightly. The major differences aresummarized in Table 9.TABLE 9:COMPARISON BETWEEN <strong>PIC18F</strong> AND <strong>PIC24F</strong> RESETSFeature Description <strong>PIC18F</strong> <strong>PIC24F</strong>Legacy Reset TypesAdditional Reset TypesBOR ConfigurationPOR, BOR, MCLR, RESET Instruction, WDT, Stack ErrorConfiguration Word Mismatch(<strong>PIC18F</strong>XXJ Flash devices)Configurable, software controllable inmany devicesIllegal Opcode/Uninitialized W,Configuration Word Mismatch, Trap ConflictTied <strong>to</strong> on-chip regula<strong>to</strong>rStack Underflow/Overflow Reset Reset Unmaskable trapSFR Reset States (1) Dependent on type of Reset Uniform for all Reset typesStart-up Timer Configurable Tied <strong>to</strong> regula<strong>to</strong>r configurationNote 1: Excluding RCON and OSCCON registers.ENHANCED EVENT REPORTINGAll <strong>PIC18F</strong> devices use a <strong>to</strong>tal of 7 flag bits <strong>to</strong> report themost immediately past Reset event. This includes5 bits in the RCON register and 2 stack event flags inthe STKPTR register. <strong>PIC18F</strong> devices, with later implementationsof nanoWatt Technology, also include acontrol bit (SBOREN), the Reset state of which can beused as an indirect flag. In all <strong>PIC18F</strong> devices, RCONflag bits are inverted sense: they are set in the absenceof the event and cleared when the event has occurred.The overlap of some bits in the indication of a particularReset state requires that all bits be assessed <strong>to</strong>determine which Reset event has just occurred.In contrast, <strong>PIC24F</strong> devices use 12 flag bits; 11 arelocated in the RCON register and one (STKERR) in theINTCON1 register. Each bit is closely associated with aparticular event, so the change of state in one bit givesa clearer idea of the event that has just occurred. Inaddition, separate Sleep and Idle flag bits are now used<strong>to</strong> indicate if the device is in one of the Power-Savingmodes. These can be used <strong>to</strong> identify exits on interruptfrom Sleep or Idle modes. All flag bits are standardsense and become set when the corresponding even<strong>to</strong>ccurs.The differences in Reset flag bits between <strong>PIC18F</strong> and<strong>PIC24F</strong> are summarized in Table 10. The specific bitstates and their corresponding Reset states arecompared in Table 11 and Table 12.TABLE 10:COMPARISON OF RESETFLAGS IN <strong>PIC18F</strong> AND <strong>PIC24F</strong>ARCHITECTURESRCON Bit Function <strong>PIC18F</strong> <strong>PIC24F</strong>MCLR Reset — EXTRSoftware Reset RI SWRPOR POR PORBOR BOR BORWDT Reset TO WDTOTrap Conflict Reset — TRAPRIllegal Operation or— IOPUWRUninitialized W RegisterConfiguration Word— CMMismatchSleep Mode PD SLEEPIdle Mode PD IDLEStack Overflow STKFUL STKERR (1)Stack Underflow STKUNF STKERR (1)Note 1: Implemented as a hardware trap rather thana Reset. See the “Interrupt Controller”section on page 17 for more details.© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 13

TABLE 11:<strong>PIC24F</strong> RESET STATUS BITS STATESConditionProgramCounterTRAPRIOPUWREXTRSWRWDTOSLEEPIDLECMBORPORSTKERRPower-on Reset 000000h 0 0 0 0 0 0 0 u 0 1 0RESET Instruction 000000h 0 0 0 1 0 0 0 u 0 0 0Brown-out Reset 000000h 0 0 0 0 0 0 0 u 1 0 0MCLR: in Run mode 000000h 0 0 1 0 0 0 0 u 0 0 0in Idle mode 000000h 0 0 1 0 0 0 1 u 0 0 0in Sleep mode 000000h 0 0 1 0 0 1 0 u 0 0 0WDT Time-out Reset: in Run mode 000000h 0 0 0 0 1 0 0 u 0 0 0in Idle mode PC + 2 0 0 0 0 1 0 1 u 0 0 0in Sleep mode PC + 2 0 0 0 0 1 1 0 u 0 0 0Stack Overflow Reset 000000h 0 0 0 0 0 0 0 u 0 0 1Stack Underflow Reset (1) 000000h 0 0 0 0 0 0 0 u 0 0 1Trap Conflict Reset (1) 000000h 1 0 0 0 0 0 0 u 0 0 0Illegal Opcode/Uninitialized WREG 000000h 0 1 0 0 0 0 0 u 0 0 0Configuration Word Mismatch Reset 000000h u u u u u u u 1 u u uInterrupt Exit: from Idle mode (2) 0 0 0 0 0 0 1 u 0 0 0from Sleep mode(2)0 0 0 0 0 1 0 u 0 0 0Idle mode (execute PWRSAV 1) PC + 2 0 0 0 0 0 0 1 u 0 0 0Sleep mode (execute PWRSAV 0) PC + 2 0 0 0 0 0 1 0 u 0 0 0Legend: u = unchangedNote 1: <strong>PIC24F</strong> stack events are trap events and not Resets; they are listed here for comparison purposes only. See the“Non-Maskable Traps” section on page 17 for more information.2: Program counter is loaded with PC + 2 if the interrupt’s priority is less than or equal <strong>to</strong> the CPU interrupt priority level, orthe interrupt’s hardware vec<strong>to</strong>r if the priority is greater than the CPU priority.TABLE 12:<strong>PIC18F</strong> COMPARABLE RESET STATUS BITS STATESRCONSTKPTRConditionProgramCounterSBOREN (1)RITOPDPORBORSTKFULSTKUNFPOR 0000h 1 1 1 1 0 0 0 0BOR 0000h u (2) 1 1 1 u 0 u uRESET Instruction 0000h u (2) 0 u u u u u uMCLR: in PRI_RUN mode 0000h u (2) u u u u u u uin SEC_RUN or RC_RUN modes 0000h u (2) u 1 u u u u uin Idle or Sleep modes 0000h u (2) u 1 0 u u u uWDT Time-out: in any Run mode 0000h u (2) u 0 u u u u uin Idle or Sleep modes PC + 2 u (2) u 0 0 u u u uStack Full Reset (STVREN = 1) 0000h u (2) u u u u u 1 uStack Underflow Reset or Error0000h u (2) u u u u u u 1(STVREN = 1 or 0)Interrupt Exit from Power-Managed modes PC + 2 (3) u (2) u u 0 u u u uLegend: u = unchangedNote 1: SBOREN is not implemented in <strong>PIC18F</strong>XXJ Flash devices, or in devices with earlier versions of nanoWatt Technology.2: Reset state is ‘1’ for Power-on Reset and unchanged for all other Resets when software Brown-out Reset is enabled(BOREN1:BOREN0 Configuration bits = 01 and SBOREN = 1); otherwise, the Reset state is ‘0’.3: When the wake-up is due <strong>to</strong> an interrupt and the GIEH or GIEL bit is set, the PC is loaded with the interrupt vec<strong>to</strong>r(008h or 0018h).DS39764A-page 14© 2006 <strong>Microchip</strong> Technology Inc.

ADDITIONAL <strong>PIC24F</strong> RESETSBeyond the legacy Reset events supported by botharchitectures, <strong>PIC24F</strong> supports three new hardwareResets:• IOPUWR: Attempted execution of anunrecognized or undetectable instruction opcode,or an attempt <strong>to</strong> use an uninitialized register as anAddress Pointer• CM: <strong>An</strong> event has caused a mismatch betweenthe Flash Configuration Words and their counterpartsin configuration space, or the device hasdetected a parity error in the Configuration Words• TRAPR: Two trap events have occurred, with thesecond taking place before the first has beenclearedThese events have no equivalent in the <strong>PIC18F</strong>architecture.STACK ERROR EVENTSIn <strong>PIC18F</strong> devices, a stack overflow or underflow eventcauses a full device Reset when the STVREN Configurationbit is programmed. Even if a stack interrupt isnot enabled, the PC is reset <strong>to</strong> zero if an event occurs.The STKFUL or STKUNF flag bit is set in either event<strong>to</strong> indicate which event has occurred.In <strong>PIC24F</strong> devices, a stack event is treated as a softtrap and causes code execution <strong>to</strong> jump <strong>to</strong> the interruptvec<strong>to</strong>r at address 000Ah. No differentiation is madebetween overflow and underflow events. <strong>PIC24F</strong> trapevents, in general, are discussed in more detail in the“Non-Maskable Traps” section on page 17.BOR CONFIGURATION<strong>PIC18F</strong> devices have always provided some level ofconfigurability for BOR. At a minimum, the BOR can beenabled or disabled, and the BOR threshold (VBOR) setduring device programming, by using the BOREN andBORV1:BORV0 Configuration bits. Later <strong>PIC18F</strong>devices with nanoWatt Technology allow the BOR <strong>to</strong> beselectively controlled in software.For <strong>PIC24F</strong> devices, the BOR function is incorporatedin<strong>to</strong> the on-chip voltage regula<strong>to</strong>r. The BOR is alwaysenabled when the regula<strong>to</strong>r is enabled, and active whileVDD is below VBOR (2.35V <strong>to</strong> 2.6V, typically). The abilityof <strong>PIC24F</strong> devices <strong>to</strong> operate at maximum frequencyacross the normal operating voltage range makes a configurableBOR unnecessary. This is in contrast <strong>to</strong> many<strong>PIC18F</strong> devices, where maximum frequency may betied <strong>to</strong> VDD, as described in the specific device datasheet. In these cases, it may be necessary <strong>to</strong> configurea BOR set point that reflects the application’s specificvoltage and frequency requirements.Note:<strong>PIC18F</strong>XXJ Flash devices, such as the<strong>PIC18F</strong>87J10, use BOR circuitry identical<strong>to</strong> <strong>PIC24F</strong> devices.SFR RESET STATESIn <strong>PIC18F</strong> devices, SFRs have up two designatedReset states: the default state on POR or BOR, and analternate state on all other legacy Resets. Dependingon the register’s function, the register values in the twostates are identical; but for many registers, the valueprior <strong>to</strong> the Reset is preserved.In <strong>PIC24F</strong> devices, there is no distinction betweenPOR/BOR and other Resets. All registers return <strong>to</strong> theiroriginal default values on a device Reset, regardless ofthe source. The only exceptions <strong>to</strong> this rule are theOSCCON and RCON registers, where the Reset valueof one or more bits is dependent on device configurationor state immediately prior <strong>to</strong> Reset.Data sheets and other literature for <strong>PIC18F</strong> devicesoften list a third Reset state: the value immediatelyfollowing a wake-up by WDT time-out or interrupt. Foralmost all registers in all <strong>PIC18F</strong> devices, the value isthe same as that immediately before the wake-upevent. For <strong>PIC24F</strong> devices, all SFRs are assumed <strong>to</strong>remain unchanged following a wake-up. Specificexceptions will be noted in the appropriate device datasheet.START-UP TIMING AFTER RESETS<strong>PIC18F</strong> devices include a fixed start-up timer that holdsthe microcontroller in a Reset state. The timer’sinterval, TPWRT, allows for the memory array <strong>to</strong>power-up and internal circuits <strong>to</strong> reach their initialstates. The power-up timer can be enabled or disabledduring device configuration by programming the PWRTConfiguration bit. Additional delays are added <strong>to</strong>TPWRT depending on the start-up oscilla<strong>to</strong>r selectedand whether or not the internal PLL is being used.For <strong>PIC24F</strong> devices, the start-up time is dependent onthe configuration of the on-chip voltage regula<strong>to</strong>r whenthe device exits a POR or BOR event. The <strong>to</strong>tal regula<strong>to</strong>rdelay is TSTARTUP, which is equal <strong>to</strong> TPWRT (if theregula<strong>to</strong>r is disabled) or TVREG (if it is enabled). TPWRTis a fixed, 64 ms nominal delay and is comparable <strong>to</strong>the <strong>PIC18F</strong> TPWRT delay; it provides time for the powersupply <strong>to</strong> stabilize. TVREG is a nominal, 10 μs delaywhich permits the internal voltage regula<strong>to</strong>r <strong>to</strong> stabilize.<strong>An</strong> additional voltage regula<strong>to</strong>r delay occurs if VREGS(RCON) is clear. Additional delays are also providedfor oscilla<strong>to</strong>r start-up and PLL, if enabled, whichare consistent with <strong>PIC18F</strong> devices. See the devicedata sheets for more information.OTHER RESET FEATURESMany <strong>PIC18F</strong> devices with later implementations ofnanoWatt Technology have a configurable MCLR pin.For these devices, the MCLRE Configuration bit canselect if the pin functions as the device Master Clear, oras an input only I/O port. <strong>PIC24F</strong> devices have “fixed”MCLR pins that cannot be reconfigured.© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 15

MIGRATION CONSIDERATIONSFor applications that require polling of Reset events,the method of polling will need <strong>to</strong> be changed. Althoughall states that were tracked in <strong>PIC18F</strong> devices are stilltrackable in <strong>PIC24F</strong>, the meaning of the legacy RCONflag bits is more narrowly defined. It is no longer necessary<strong>to</strong> read all flags <strong>to</strong> interpret the immediatelyprevious event; for most cases, it will only be necessary<strong>to</strong> see which flag bit is now set. Note that the <strong>PIC24F</strong>RCON status bits are active-high and <strong>PIC18F</strong> RCONbits are active-low.Be aware that the start-up time of the device increaseswhen the regula<strong>to</strong>r is disabled <strong>to</strong> permit the applicationvoltage <strong>to</strong> stabilize. Enabling the regula<strong>to</strong>r also enablesthe BOR function.Note:The internal regula<strong>to</strong>r should not be used<strong>to</strong> power circuitry outside of the device. It isintended for internal power consumptiononly.It is recommended for both architectures <strong>to</strong> connectMCLR <strong>to</strong> VDD using a 1 kΩ resis<strong>to</strong>r. This will limit thecurrent flow in<strong>to</strong> the MCLR pin due <strong>to</strong> potential externaloverstresses.DS39764A-page 16© 2006 <strong>Microchip</strong> Technology Inc.

Interrupt ControllerThe <strong>PIC24F</strong> interrupt controller contains manyimproved interrupt options compared <strong>to</strong> the <strong>PIC18F</strong>.These new features include, but are not limited <strong>to</strong>,increased processor exceptions, software traps anduser-selectable priority levels. Table 13 summarizesthe differences between the <strong>PIC18F</strong> and <strong>PIC24F</strong>interrupts.TABLE 13:COMPARISON BETWEEN <strong>PIC18F</strong> AND <strong>PIC24F</strong> INTERRUPT CONTROLLERSInterrupt Features <strong>PIC18F</strong> <strong>PIC24F</strong>Unique Interrupt Flag and Enable for each Source Yes YesGlobal Interrupt Enable Yes YesSoftware Clearable Interrupt Flags Yes YesFlags Set Regardless if Interrupt is Enabled or Disabled Yes YesSoftware can Generate any Peripheral Interrupt Yes YesAu<strong>to</strong>matic Context Save/Res<strong>to</strong>re Yes YesExits Power-Managed Modes Yes YesAssignable Interrupt Priority high or low 8 levels, user-definedLatency for External Interrupt Events (INTx pins or the3 or 4 TCY 5 TCY (Fixed)PORTB input change interrupt)Priority Exit from Sleep and Idle Modes No YesInterrupt Nesting Disable Option No YesSoftware Selectable Core Interrupt Priority Level No YesTrap Vec<strong>to</strong>rs No Yes (4)Unique Interrupt/Trap Source No YesAlternate Interrupt Vec<strong>to</strong>r Table for Emulation No YesNatural priority Unmaskable or Non-Maskable Interrupts No YesCapable of Disabling Interrupts for Specific Number of TCY No YesNEW <strong>PIC24F</strong> INTERRUPT FEATURES• Unique Interrupt and Trap Vec<strong>to</strong>rs: Eachindividual interrupt source is assigned in hardwarea natural priority, allowing interrupts <strong>to</strong> be sortedwith no additional user intervention, as well as aunique interrupt vec<strong>to</strong>r• User-Assignable Priority: Users can also giveeach interrupt one of eight levels of priority, whichcan be used <strong>to</strong> override the natural priority• Software Assigned Core Priority: Users canalso set a threshold priority level at which theCPU will respond <strong>to</strong> interrupts• Interrupt Nesting: The use of natural priority anduser-assigned priority allows multiple interruptevents <strong>to</strong> be nested; this feature can also beselectively disabled• Hard and Soft Traps: Up <strong>to</strong> 8 non-maskable hardtraps with high natural priority are provided <strong>to</strong> flagpotentially serious events, such as math (divideby 0), stack overflow/underflow, address or dataalignment and oscilla<strong>to</strong>r failure• Alternate Vec<strong>to</strong>r Table: Allows for a convenientswitch between support and applicationenvironments without reprogramming• Priority Exit From Power-Saving modes:Allows the application <strong>to</strong> either resume normalcode execution, or jump <strong>to</strong> an ISR, depending onthe interrupt priority levelNote: For further information on traps, refer <strong>to</strong>the specific device data sheet.UNSUPPORTED <strong>PIC18F</strong> FEATURESAll <strong>PIC18F</strong> interrupt controller features are supported inthe <strong>PIC24F</strong> interrupt controller.NON-MASKABLE TRAPSIn <strong>PIC24F</strong> architecture, there are four hardware trapevents with interrupts that can never be disabled:• Address Decode Error• Oscilla<strong>to</strong>r Failure• Stack Error• Math (Overflow) Error© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 17

These errors always force an immediate jump <strong>to</strong>specific interrupt vec<strong>to</strong>rs. The two most serious errors(Address Decode and Oscilla<strong>to</strong>r Failure) are hardtraps; these must be cleared before the CPU executioncan continue. All traps have their own individual flag bit.In addition <strong>to</strong> these unmaskable events, the <strong>PIC24F</strong>architecture can be expanded at a future time <strong>to</strong>include up <strong>to</strong> four additional traps.<strong>PIC18F</strong> architecture does not have an equivalent <strong>to</strong> thehardware trap. <strong>PIC18F</strong> stack error events are treatedas Resets.BIT NAME CHANGES AND MAPPING<strong>PIC24F</strong> devices maintain the same general nomenclaturefor interrupt bit names as <strong>PIC18F</strong> devices, with twoimportant differences. Both families maintain interruptenable, flag and priority bits that are generically namedxxxIE, xxxIF and xxxIP (where ’xxx’ is the mnemonic forthe interrupt source).The first major difference is the presence of three interruptpriority bits for each source, instead of the oneused for <strong>PIC18F</strong> devices. These bits, genericallynamed xxxIP2 through xxxIP0, allow the interrupt <strong>to</strong> beassigned one of eight relative priority levels.The other difference is the number of interrupt sources.While many interrupts have the same (or very similar)name as <strong>PIC18F</strong> devices, others are new. Other interruptshave similar names but have a different meaningfrom their <strong>PIC18F</strong> counterparts. Users should refer <strong>to</strong>the appropriate <strong>PIC24F</strong> device data sheet for acomplete list of interrupts and their meanings.SETUP AND ENABLING INTERRUPTSTo set up and enable interrupts on <strong>PIC18F</strong> devices:Required Steps:1. Clear the interrupt flag status bit associated withthe peripheral in the associated PIRx orINTCONx register.2. Enable the interrupt source by setting the interruptenable control bit associated with the sourcein the appropriate PIEx or INTCONx register.Note: The interrupt flag still needs <strong>to</strong> be clearedprior <strong>to</strong> exiting an ISR.Optional Step:Select the user-assigned priority level for the interruptsource by writing <strong>to</strong> the control bits in the RCON register;select high priority or low priority using the priority bit inthe corresponding IPRx register. The interrupt priorityfeature is enabled by setting the IPEN bit (RCON).To set up and enable interrupts on <strong>PIC24F</strong> devices:Required Steps:1. Set the NSTDIS bit (INTCON1) if nestedinterrupts are not desired.2. Clear the interrupt flag status bit associated withthe peripheral in the associated IFSx register.3. Enable the interrupt source by setting the interruptenable control bit associated with thesource in the appropriate IECx register.Note:Optional Step:Select the user-assigned priority level for the interruptsource by writing the control bits in the appropriate IPCxregister. The priority level will depend on the specificapplication and type of interrupt source. If multiple prioritylevels are not desired, the IPCx register control bit forall enabled interrupt sources may be programmed <strong>to</strong> thesame non-zero value.Note:The Interrupt/trap flag still needs <strong>to</strong> becleared prior <strong>to</strong> exiting an ISR.Upon Reset, all interrupts are assigned adefault priority level of 4.DISABLING USER INTERRUPTSTo disable interrupts on <strong>PIC18F</strong> devices, it is onlynecessary <strong>to</strong> clear the GIE bit (GIEH or GIEL if prioritylevels are used).To disable user interrupts on <strong>PIC24F</strong> devices, thesesteps are required:1. Push the current STATUS register value on<strong>to</strong>the software stack using the PUSH instruction.2. Force the CPU <strong>to</strong> priority level 7 by inclusiveORing the value OEh with the low byte of theSTATUS register (SRL). To enable user interrupts,the POP instruction may be used <strong>to</strong> res<strong>to</strong>rethe previous STATUS register value.Note: The DISI instruction allows interrupts ofpriority levels 1-6 <strong>to</strong> be disabled for a fixedperiod of time.MIGRATION CONSIDERATIONS<strong>PIC18F</strong> architecture only has the ability <strong>to</strong> assign eitherhigh or low priority interrupts <strong>to</strong> individual sources.<strong>PIC24F</strong> architecture allows the assignment of multiplepriority levels for interrupts (priorities 0 through 7 areuser defined and priorities 8 through 15 are hardwaredefined). At the very least, interrupts in native <strong>PIC18F</strong>applications will need <strong>to</strong> be re-assessed, and theirpriority levels redefined in <strong>PIC24F</strong> terms.For both <strong>PIC18F</strong> and <strong>PIC24F</strong> devices, the RETFIEinstruction exits an Interrupt Service Routine (ISR), butthis instruction does behave slightly different dependingon the microcontroller. For <strong>PIC18F</strong>, this instructionwill set the GIE bit <strong>to</strong> re-enable global interrupts. Sincethe GIE bit does not exist for <strong>PIC24F</strong>, this instructionwill res<strong>to</strong>re the previous priority level.DS39764A-page 18© 2006 <strong>Microchip</strong> Technology Inc.

Oscilla<strong>to</strong>rThe <strong>PIC24F</strong> oscilla<strong>to</strong>r system supports many of thefeatures of <strong>PIC18F</strong> nanoWatt Technology, and addsseveral new features. Both architectures support threemajor clock sources: primary oscilla<strong>to</strong>rs, internal RCoscilla<strong>to</strong>rs and 4x PLL frequency multipliers. In addition,both also support features <strong>to</strong> enhance applicationrobustness, such as software-controlled clock switching,Fail-Safe Clock Moni<strong>to</strong>rs and Two-Speed Start-up.<strong>PIC24F</strong> devices increase the flexibility of initial clockconfiguration, software controlled clock switching andthe use of the PLL.Although there are many similarities between <strong>PIC24F</strong>and <strong>PIC18F</strong> architectures in the oscilla<strong>to</strong>r and clockgeneration, there are also important differences in theimplementation of these features. Because the oscilla<strong>to</strong>raffects most aspects of an application, it is important<strong>to</strong> understand the differences before migrating anapplication <strong>to</strong> a <strong>PIC24F</strong> device.The major differences between the <strong>PIC18F</strong> and<strong>PIC24F</strong> clock structures are detailed in Table 14.CHANGES FROM <strong>PIC18F</strong> ARCHITECTUREFeatures added from the <strong>PIC18F</strong> implementation ofnanoWatt Technology include:• Enhanced PLL Operation: <strong>PIC24F</strong> architectureallows the PLL <strong>to</strong> be used under software control inall modes where it is available, and makes the PLLavailable <strong>to</strong> all External Primary Oscilla<strong>to</strong>r modes.• Doze Mode: This permits differential clocking ofthe CPU and peripherals, and allows the CPU <strong>to</strong>run at lower speeds while maintaining timingsensitive peripherals (see the “Power-SavingFeatures” section on page 23 for more details).<strong>PIC18F</strong> features that are no longer supported in<strong>PIC24F</strong> architecture include:• LP and External RC Primary Oscilla<strong>to</strong>r modeshave been removed in favor of SOSC and FRCOscilla<strong>to</strong>r modes• XT mode is still implemented, but is limited <strong>to</strong> theupper end of the upper range of frequenciesavailable with <strong>PIC18F</strong> devices. For <strong>PIC24F</strong>devices, the XT frequency range is 3.5 MHz <strong>to</strong>10 MHz.TABLE 14:COMPARISON OF MAJOR OSCILLATOR FEATURESFeature Description <strong>PIC18F</strong> <strong>PIC24F</strong>Primary (External) Oscilla<strong>to</strong>r ModesHS, XT, EC, LP andexternal RC (1)HS, XT and EC(all devices)Secondary (Timer1) Oscilla<strong>to</strong>r Yes Yes (SOSC)8 MHz Internal RC Oscilla<strong>to</strong>r Most devices (INTOSC) (1) Yes (FRC)31 kHz Internal RC Oscilla<strong>to</strong>r Yes (INTRC) Yes (LPRC)4x PLL Options:XTPLL (MSPLL)ECPLLINTOSCPLL/FRCPLLNoSelect devices onlySelect devices onlyINTOSC/FRC Tuning 5-bit magnitude, ±12% range 6-bit magnitude, ±12% rangeSoftware Clock Switching Between clock sources only Between all available oscilla<strong>to</strong>r types;uses safety interlockDoze Mode No YesFail-Safe Clock Moni<strong>to</strong>r Yes YesTwo-Speed Start-up Yes YesNote 1: Applies <strong>to</strong> most <strong>PIC18F</strong>XXXX devices, such as <strong>PIC18F</strong>8722. Currently, <strong>PIC18F</strong>XXJ Flash devices, suchas the <strong>PIC18F</strong>87J10, only offer HS and EC Primary Oscilla<strong>to</strong>r modes and no INTOSC oscilla<strong>to</strong>r.YesYesYes© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 19

BIT AND CONTROL FUNCTION MAPPINGThere is not a precise one-<strong>to</strong>-one correspondencebetween configuration and control functions of the<strong>PIC18F</strong> and <strong>PIC24F</strong> architectures. The most commondifferences are shown in Table 15. Details arediscussed later in this section.TABLE 15:COMPARISON OF OSCILLATOR BIT AND CONTROL FUNCTION MAPPINGOscilla<strong>to</strong>r Block Function <strong>PIC18F</strong> <strong>PIC24F</strong>Define Start-up Oscilla<strong>to</strong>rDefine Primary Oscilla<strong>to</strong>r TypeDefine I/O Port Functions in EC Oscilla<strong>to</strong>rModesFOSC3:FOSC0(CONFIG1H) (1)FNOSC2:FNOSC0(Configuration Word 2)POSCMD1:POSCMD0(Configuration Word 2)OSCIOFCN(Configuration Word 2)Enable Secondary Oscilla<strong>to</strong>r T1OSCEN (T1CON) SOSCEN (OSCCON)Select INTOSC/FRC Postscaler IRCF2:IRCF0 (OSCCON) RCDIV2:RCDIV0 (CLKDIV)Switch Run-Time Clock SourceSCS1:SCS0 (OSCCON)NOSC2:NOSC0, OSWEN(OSCCON), FCKSM0(Configuration Word 2)Active Clock Source Moni<strong>to</strong>ring OSTS, IOFS, T1RUN COSC2:COSC0Enable Two-Speed Start-up IESO (CONFIG1H) IESO (Configuration Word 2)Enable Fail-Safe Clock Moni<strong>to</strong>rFCKSM1:FCKSM0FCMEN (CONFIG1H)(Configuration Word 2)Note 1: <strong>PIC18F</strong>XXXX devices only; FOSC2:FOSC0 (CONFIG2H) on current <strong>PIC18F</strong>XXJ Flash devices.PRIMARY OSCILLATORS (POSC)<strong>PIC18F</strong> microcontrollers, with the latest versions ofnanoWatt Technology, use an oscilla<strong>to</strong>r circuit that supportsa wide range of external components, including avariety of crystals, RC networks or external clock genera<strong>to</strong>rs.To use the oscilla<strong>to</strong>r, users connect their crystal orRC circuit <strong>to</strong> the OSC1 and OSC2 pins, or present theexternal clock on OSC1. The exact oscilla<strong>to</strong>r mode <strong>to</strong> beused is selected during device configuration using theFOSC3:FOSC0 Configuration bits, and must match theactual external circuit <strong>to</strong> be used.<strong>PIC24F</strong> microcontrollers support a similar range ofoscilla<strong>to</strong>r options on the OSC1 and OSC2 pins;however, the options for support of low-power,low-frequency crystals and external RC resonantcircuits have been omitted. These have been replacedby the use of a high-speed internal RC oscilla<strong>to</strong>r, andthe use of the Timer1 oscilla<strong>to</strong>r in the more flexibleclock structure.The primary oscilla<strong>to</strong>r mode is selected during configurationwith a combination of the FNOSC2:FNOSC0 andPOSCMD Configuration bits. Like <strong>PIC18F</strong>devices, the configuration must match the externalcircuit <strong>to</strong> be used in the application.SECONDARY OSCILLATOR (SOSC)All <strong>PIC18F</strong> devices have the option <strong>to</strong> use the Timer1oscilla<strong>to</strong>r as a secondary clock source. The mosttypical arrangement for this option is <strong>to</strong> connect alow-power, 32 kHz watch crystal across pins T1OSIand T1OSO. The oscilla<strong>to</strong>r is controlled separatelyfrom the device clock controls with the T1OSCEN bit(T1CON).<strong>PIC24F</strong> devices also provide a secondary oscilla<strong>to</strong>rthat is identical in function <strong>to</strong> the Timer1 oscilla<strong>to</strong>r; i<strong>to</strong>nly differs in that it is controlled through the OSCCONregister with the SOSCEN bit. The crystal input/outputpins are renamed SOSCI and SOSCO.The <strong>PIC24F</strong> secondary oscilla<strong>to</strong>r takes the place of thePrimary LP Oscilla<strong>to</strong>r mode provided on <strong>PIC18F</strong>devices, but not supported on <strong>PIC24F</strong>. To use SOSC asthe default oscilla<strong>to</strong>r on start-up, it must by selected indevice configuration by the FNOSC2:FNOSC0 bits andenabled in software by setting the SOSCEN bit.DS39764A-page 20© 2006 <strong>Microchip</strong> Technology Inc.