PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

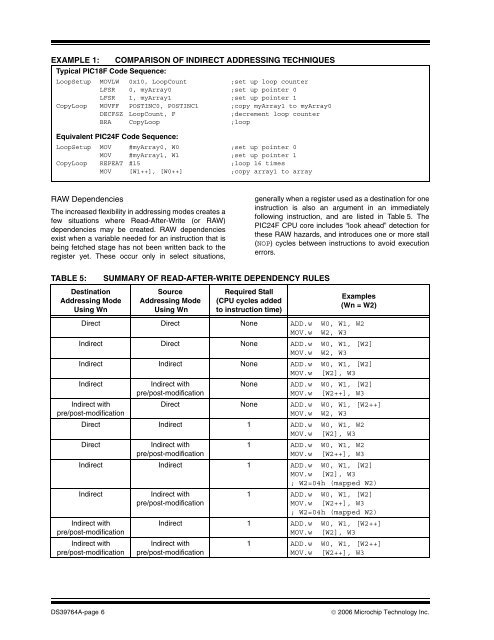

EXAMPLE 1: COMPARISON OF INDIRECT ADDRESSING TECHNIQUESTypical <strong>PIC18F</strong> Code Sequence:LoopSetup MOVLW 0x10, LoopCount ;set up loop counterLFSR 0, myArray0 ;set up pointer 0LFSR 1, myArray1 ;set up pointer 1CopyLoop MOVFF POSTINC0, POSTINC1 ;copy myArray1 <strong>to</strong> myArray0DECFSZ LoopCount, F ;decrement loop counterBRA CopyLoop ;loopEquivalent <strong>PIC24F</strong> Code Sequence:LoopSetup MOV #myArray0, W0 ;set up pointer 0MOV #myArray1, W1 ;set up pointer 1CopyLoop REPEAT #15 ;loop 16 timesMOV [W1++], [W0++] ;copy array1 <strong>to</strong> arrayRAW DependenciesThe increased flexibility in addressing modes creates afew situations where Read-After-Write (or RAW)dependencies may be created. RAW dependenciesexist when a variable needed for an instruction that isbeing fetched stage has not been written back <strong>to</strong> theregister yet. These occur only in select situations,generally when a register used as a destination for oneinstruction is also an argument in an immediatelyfollowing instruction, and are listed in Table 5. The<strong>PIC24F</strong> CPU core includes “look ahead” detection forthese RAW hazards, and introduces one or more stall(NOP) cycles between instructions <strong>to</strong> avoid executionerrors.TABLE 5:SUMMARY OF READ-AFTER-WRITE DEPENDENCY RULESDestinationAddressing ModeUsing WnSourceAddressing ModeUsing WnRequired Stall(CPU cycles added<strong>to</strong> instruction time)Examples(Wn = W2)Direct Direct None ADD.w W0, W1, W2MOV.w W2, W3Indirect Direct None ADD.w W0, W1, [W2]MOV.w W2, W3Indirect Indirect None ADD.w W0, W1, [W2]MOV.w [W2], W3IndirectIndirect withpre/post-modificationIndirect withpre/post-modificationNoneADD.w W0, W1, [W2]MOV.w [W2++], W3Direct None ADD.w W0, W1, [W2++]MOV.w W2, W3Direct Indirect 1 ADD.w W0, W1, W2MOV.w [W2], W3DirectIndirect withpre/post-modification1 ADD.w W0, W1, W2MOV.w [W2++], W3Indirect Indirect 1 ADD.w W0, W1, [W2]MOV.w [W2], W3; W2=04h (mapped W2)IndirectIndirect withpre/post-modificationIndirect withpre/post-modificationIndirect withpre/post-modification1 ADD.w W0, W1, [W2]MOV.w [W2++], W3; W2=04h (mapped W2)Indirect 1 ADD.w W0, W1, [W2++]MOV.w [W2], W3Indirect withpre/post-modification1 ADD.w W0, W1, [W2++]MOV.w [W2++], W3DS39764A-page 6© 2006 <strong>Microchip</strong> Technology Inc.