PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

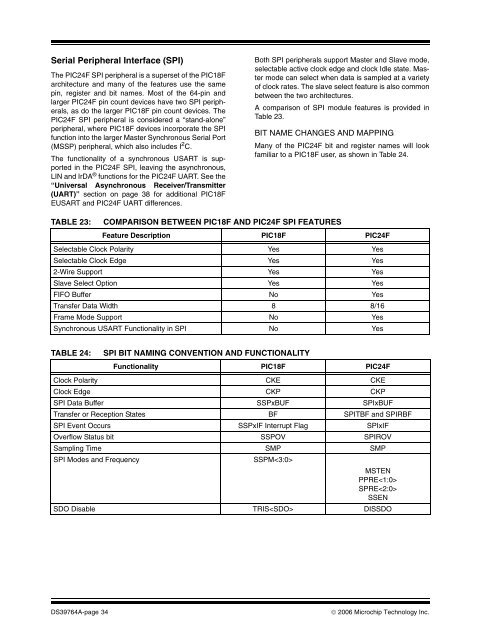

Serial Peripheral Interface (SPI)The <strong>PIC24F</strong> SPI peripheral is a superset of the <strong>PIC18F</strong>architecture and many of the features use the samepin, register and bit names. Most of the 64-pin andlarger <strong>PIC24F</strong> pin count devices have two SPI peripherals,as do the larger <strong>PIC18F</strong> pin count devices. The<strong>PIC24F</strong> SPI peripheral is considered a “stand-alone”peripheral, where <strong>PIC18F</strong> devices incorporate the SPIfunction in<strong>to</strong> the larger Master Synchronous Serial Port(MSSP) peripheral, which also includes I 2 C.The functionality of a synchronous USART is supportedin the <strong>PIC24F</strong> SPI, leaving the asynchronous,LIN and IrDA ® functions for the <strong>PIC24F</strong> UART. See the“Universal Asynchronous Receiver/Transmitter(UART)” section on page 38 for additional <strong>PIC18F</strong>EUSART and <strong>PIC24F</strong> UART differences.Both SPI peripherals support Master and Slave mode,selectable active clock edge and clock Idle state. Mastermode can select when data is sampled at a varietyof clock rates. The slave select feature is also commonbetween the two architectures.A comparison of SPI module features is provided inTable 23.BIT NAME CHANGES AND MAPPINGMany of the <strong>PIC24F</strong> bit and register names will lookfamiliar <strong>to</strong> a <strong>PIC18F</strong> user, as shown in Table 24.TABLE 23: COMPARISON BETWEEN <strong>PIC18F</strong> AND <strong>PIC24F</strong> SPI FEATURESFeature Description <strong>PIC18F</strong> <strong>PIC24F</strong>Selectable Clock Polarity Yes YesSelectable Clock Edge Yes Yes2-Wire Support Yes YesSlave Select Option Yes YesFIFO Buffer No YesTransfer Data Width 8 8/16Frame Mode Support No YesSynchronous USART Functionality in SPI No YesTABLE 24:SPI BIT NAMING CONVENTION AND FUNCTIONALITYFunctionality <strong>PIC18F</strong> <strong>PIC24F</strong>Clock Polarity CKE CKEClock Edge CKP CKPSPI Data Buffer SSPxBUF SPIxBUFTransfer or Reception States BF SPITBF and SPIRBFSPI Event Occurs SSPxIF Interrupt Flag SPIxIFOverflow Status bit SSPOV SPIROVSampling Time SMP SMPSPI Modes and FrequencySSPMMSTENPPRESPRESSENSDO Disable TRIS DISSDODS39764A-page 34© 2006 <strong>Microchip</strong> Technology Inc.