PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

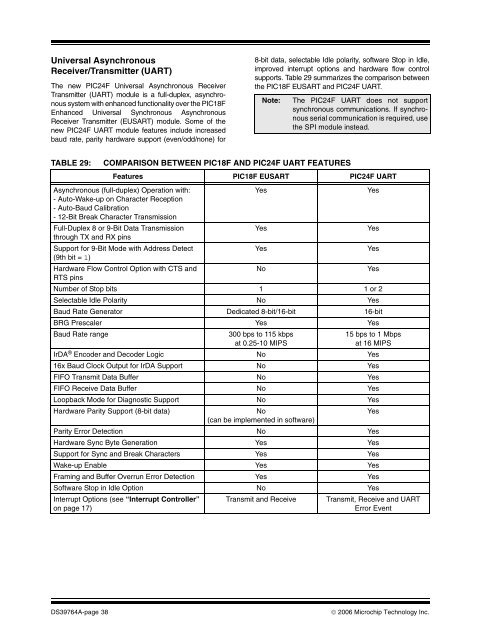

Universal AsynchronousReceiver/Transmitter (UART)The new <strong>PIC24F</strong> Universal Asynchronous ReceiverTransmitter (UART) module is a full-duplex, asynchronoussystem with enhanced functionality over the <strong>PIC18F</strong>Enhanced Universal Synchronous AsynchronousReceiver Transmitter (EUSART) module. Some of thenew <strong>PIC24F</strong> UART module features include increasedbaud rate, parity hardware support (even/odd/none) for8-bit data, selectable Idle polarity, software S<strong>to</strong>p in Idle,improved interrupt options and hardware flow controlsupports. Table 29 summarizes the comparison betweenthe <strong>PIC18F</strong> EUSART and <strong>PIC24F</strong> UART.Note:The <strong>PIC24F</strong> UART does not supportsynchronous communications. If synchronousserial communication is required, usethe SPI module instead.TABLE 29:COMPARISON BETWEEN <strong>PIC18F</strong> AND <strong>PIC24F</strong> UART FEATURESFeatures <strong>PIC18F</strong> EUSART <strong>PIC24F</strong> UARTAsynchronous (full-duplex) Operation with:- Au<strong>to</strong>-Wake-up on Character Reception- Au<strong>to</strong>-Baud Calibration- 12-Bit Break Character TransmissionFull-Duplex 8 or 9-Bit Data TransmissionYesYesthrough TX and RX pinsSupport for 9-Bit Mode with Address DetectYesYes(9th bit = 1)Hardware Flow Control Option with CTS andNoYesRTS pinsNumber of S<strong>to</strong>p bits 1 1 or 2Selectable Idle Polarity No YesBaud Rate Genera<strong>to</strong>r Dedicated 8-bit/16-bit 16-bitBRG Prescaler Yes YesBaud Rate rangeYes300 bps <strong>to</strong> 115 kbpsat 0.25-10 MIPSYes15 bps <strong>to</strong> 1 Mbpsat 16 MIPSIrDA ® Encoder and Decoder Logic No Yes16x Baud Clock Output for IrDA Support No YesFIFO Transmit Data Buffer No YesFIFO Receive Data Buffer No YesLoopback Mode for Diagnostic Support No YesHardware Parity Support (8-bit data)NoYes(can be implemented in software)Parity Error Detection No YesHardware Sync Byte Generation Yes YesSupport for Sync and Break Characters Yes YesWake-up Enable Yes YesFraming and Buffer Overrun Error Detection Yes YesSoftware S<strong>to</strong>p in Idle Option No YesInterrupt Options (see “Interrupt Controller”on page 17)Transmit and ReceiveTransmit, Receive and UARTError EventDS39764A-page 38© 2006 <strong>Microchip</strong> Technology Inc.