PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

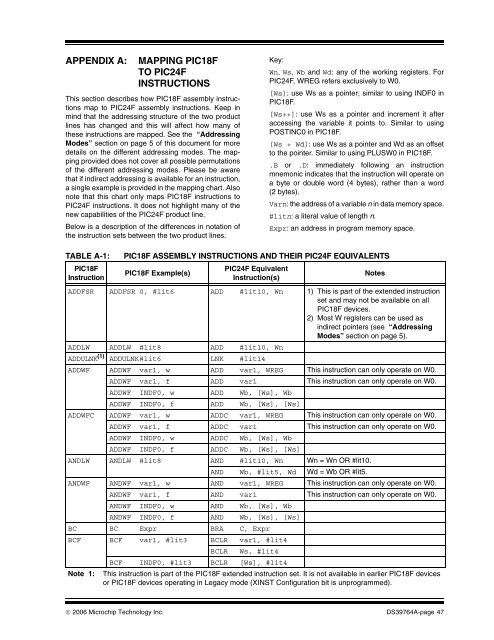

APPENDIX A:MAPPING <strong>PIC18F</strong>TO <strong>PIC24F</strong>INSTRUCTIONSThis section describes how <strong>PIC18F</strong> assembly instructionsmap <strong>to</strong> <strong>PIC24F</strong> assembly instructions. Keep inmind that the addressing structure of the two productlines has changed and this will affect how many ofthese instructions are mapped. See the “AddressingModes” section on page 5 of this document for moredetails on the different addressing modes. The mappingprovided does not cover all possible permutationsof the different addressing modes. Please be awarethat if indirect addressing is available for an instruction,a single example is provided in the mapping chart. Alsonote that this chart only maps <strong>PIC18F</strong> instructions <strong>to</strong><strong>PIC24F</strong> instructions. It does not highlight many of thenew capabilities of the <strong>PIC24F</strong> product line.Below is a description of the differences in notation ofthe instruction sets between the two product lines.Key:Wn, Ws, Wb and Wd: any of the working registers. For<strong>PIC24F</strong>, WREG refers exclusively <strong>to</strong> W0.[Ws]: use Ws as a pointer; similar <strong>to</strong> using INDF0 in<strong>PIC18F</strong>.[Ws++]: use Ws as a pointer and increment it afteraccessing the variable it points <strong>to</strong>. Similar <strong>to</strong> usingPOSTINC0 in <strong>PIC18F</strong>.[Ws + Wd]: use Ws as a pointer and Wd as an offset<strong>to</strong> the pointer. Similar <strong>to</strong> using PLUSW0 in <strong>PIC18F</strong>..B or .D: immediately following an instructionmnemonic indicates that the instruction will operate ona byte or double word (4 bytes), rather than a word(2 bytes).Varn: the address of a variable n in data memory space.#litn: a literal value of length n.Expr: an address in program memory space.TABLE A-1:<strong>PIC18F</strong>Instruction<strong>PIC18F</strong> ASSEMBLY INSTRUCTIONS AND THEIR <strong>PIC24F</strong> EQUIVALENTS<strong>PIC18F</strong> Example(s)<strong>PIC24F</strong> EquivalentInstruction(s)NotesADDFSR ADDFSR 0, #lit6 ADD #lit10, Wn 1) This is part of the extended instructionset and may not be available on all<strong>PIC18F</strong> devices.2) Most W registers can be used asindirect pointers (see “AddressingModes” section on page 5).ADDLW ADDLW #lit8 ADD #lit10, WnADDULNK (1) ADDULNK#lit6 LNK #lit14ADDWF ADDWF var1, w ADD var1, WREG This instruction can only operate on W0.ADDWF var1, f ADD var1 This instruction can only operate on W0.ADDWF INDF0, w ADD Wb, [Ws], WbADDWF INDF0, f ADD Wb, [Ws], [Ws]ADDWFC ADDWF var1, w ADDC var1, WREG This instruction can only operate on W0.ADDWF var1, f ADDC var1 This instruction can only operate on W0.ADDWF INDF0, w ADDC Wb, [Ws], WbADDWF INDF0, f ADDC Wb, [Ws], [Ws]ANDLW ANDLW #lit8 AND #lit10, Wn Wn = Wn OR #lit10.AND Wb, #lit5, Wd Wd = Wb OR #lit5.ANDWF ANDWF var1, w AND var1, WREG This instruction can only operate on W0.ANDWF var1, f AND var1 This instruction can only operate on W0.ANDWF INDF0, w AND Wb, [Ws], WbANDWF INDF0, f AND Wb, [Ws], [Ws]BC BC Expr BRA C, ExprBCF BCF var1, #lit3 BCLR var1, #lit4BCLR Ws, #lit4BCF INDF0, #lit3 BCLR [Ws], #lit4Note 1: This instruction is part of the <strong>PIC18F</strong> extended instruction set. It is not available in earlier <strong>PIC18F</strong> devicesor <strong>PIC18F</strong> devices operating in Legacy mode (XINST Configuration bit is unprogrammed).© 2006 <strong>Microchip</strong> Technology Inc. DS39764A-page 47