Carbon GIC PL390 Model User Guide for SoC Designer Plus

Carbon GIC PL390 Model User Guide for SoC Designer Plus

Carbon GIC PL390 Model User Guide for SoC Designer Plus

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

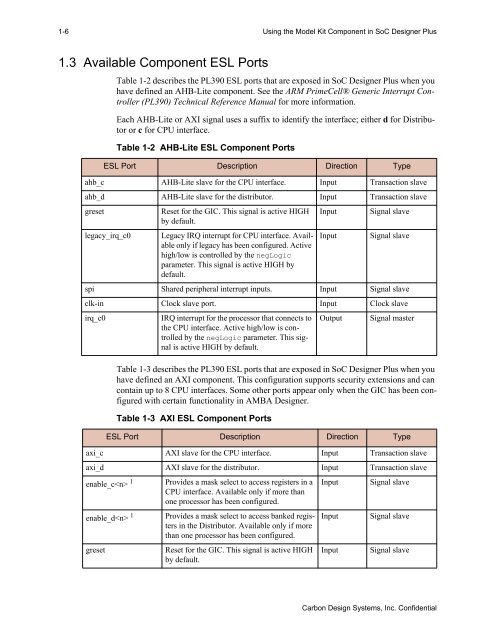

1-6 Using the <strong>Model</strong> Kit Component in <strong>SoC</strong> <strong>Designer</strong> <strong>Plus</strong>1.3 Available Component ESL PortsTable 1-2 describes the <strong>PL390</strong> ESL ports that are exposed in <strong>SoC</strong> <strong>Designer</strong> <strong>Plus</strong> when youhave defined an AHB-Lite component. See the ARM PrimeCell® Generic Interrupt Controller(<strong>PL390</strong>) Technical Reference Manual <strong>for</strong> more in<strong>for</strong>mation.Each AHB-Lite or AXI signal uses a suffix to identify the interface; either d <strong>for</strong> Distributoror c <strong>for</strong> CPU interface.Table 1-2 AHB-Lite ESL Component PortsESL Port Description Direction Typeahb_c AHB-Lite slave <strong>for</strong> the CPU interface. Input Transaction slaveahb_d AHB-Lite slave <strong>for</strong> the distributor. Input Transaction slavegresetReset <strong>for</strong> the <strong>GIC</strong>. This signal is active HIGH Input Signal slaveby default.legacy_irq_c0 Legacy IRQ interrupt <strong>for</strong> CPU interface. Availableonly if legacy has been configured. Activehigh/low is controlled by the negLogicparameter. This signal is active HIGH bydefault.Input Signal slavespi Shared peripheral interrupt inputs. Input Signal slaveclk-in Clock slave port. Input Clock slaveirq_c0IRQ interrupt <strong>for</strong> the processor that connects tothe CPU interface. Active high/low is controlledby the negLogic parameter. This signalis active HIGH by default.Output Signal masterTable 1-3 describes the <strong>PL390</strong> ESL ports that are exposed in <strong>SoC</strong> <strong>Designer</strong> <strong>Plus</strong> when youhave defined an AXI component. This configuration supports security extensions and cancontain up to 8 CPU interfaces. Some other ports appear only when the <strong>GIC</strong> has been configuredwith certain functionality in AMBA <strong>Designer</strong>.Table 1-3 AXI ESL Component PortsESL Port Description Direction Typeaxi_c AXI slave <strong>for</strong> the CPU interface. Input Transaction slaveaxi_d AXI slave <strong>for</strong> the distributor. Input Transaction slaveenable_c 1 Provides a mask select to access registers in aCPU interface. Available only if more thanone processor has been configured.Input Signal slaveenable_d 1gresetProvides a mask select to access banked registersin the Distributor. Available only if morethan one processor has been configured.Reset <strong>for</strong> the <strong>GIC</strong>. This signal is active HIGHby default.InputInputSignal slaveSignal slave<strong>Carbon</strong> Design Systems, Inc. Confidential