NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Philips Semiconductors<br />

80C51 <strong>Family</strong> Derivatives 8XC552/562 overview<br />

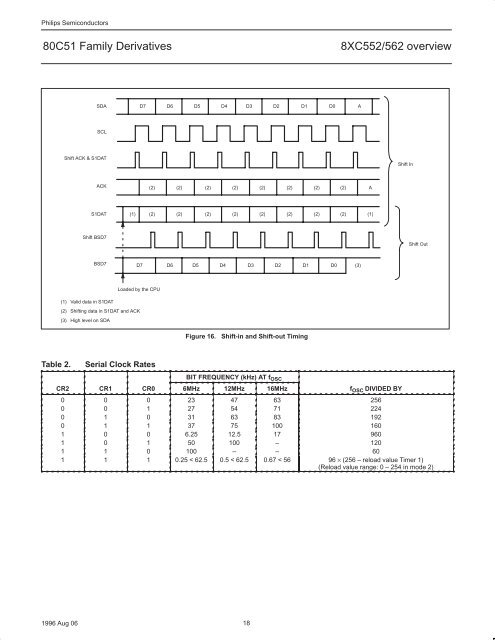

SDA<br />

SCL<br />

Shift ACK & S1DAT<br />

D7 D6 D5 D4 D3 D2 D1 D0 A<br />

ACK (2) (2) (2) (2) (2) (2) (2) (2) A<br />

S1DAT<br />

Shift BSD7<br />

(1)<br />

1996 Aug 06 18<br />

(2) (2) (2) (2) (2) (2) (2) (2) (1)<br />

BSD7 D7 D6 D5 D4 D3 D2 D1 D0 (3)<br />

Loaded by the CPU<br />

(1) Valid data in S1DAT<br />

(2) Shifting data in S1DAT and ACK<br />

(3) High level on SDA<br />

Figure 16. Shift-in and Shift-out Timing<br />

Table 2. Serial Clock Rates<br />

BIT FREQUENCY (kHz) AT fOSC CR2 CR1 CR0 6MHz 12MHz 16MHz fOSC DIVIDED BY<br />

Shift In<br />

Shift Out<br />

0 0 0 23 47 63 256<br />

0 0 1 27 54 71 224<br />

0 1 0 31 63 <strong>83</strong> 192<br />

0 1 1 37 75 100 160<br />

1 0 0 6.25 12.5 17 960<br />

1 0 1 50 100 – 120<br />

1 1 0 100 – – 60<br />

1 1 1 0.25 < 62.5 0.5 < 62.5 0.67 < 56 96 × (256 – reload value Timer 1)<br />

(Reload value range: 0 – 254 in mode 2)