NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Philips Semiconductors<br />

80C51 <strong>Family</strong> Derivatives 8XC552/562 overview<br />

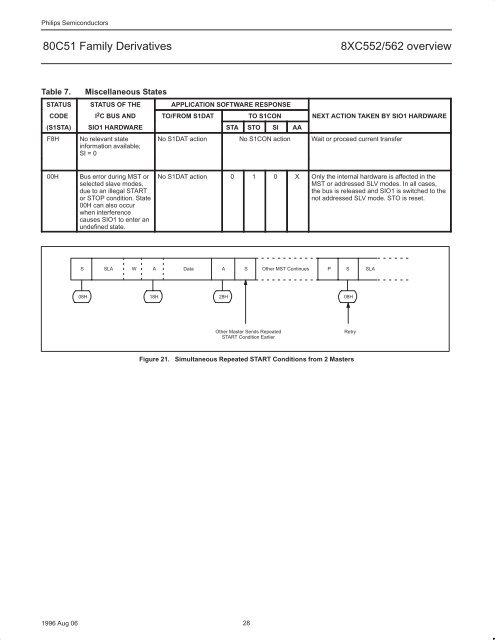

Table 7. Miscellaneous States<br />

STATUS STATUS OF THE APPLICATION SOFTWARE RESPONSE<br />

CODE I 2 C BUS AND TO/FROM S1DAT TO S1CON NEXT ACTION TAKEN BY SIO1 HARDWARE<br />

(S1STA) SIO1 HARDWARE STA STO SI AA<br />

F8H No relevant state<br />

information available;<br />

SI = 0<br />

00H Bus error during MST or<br />

selected slave modes,<br />

due to an illegal START<br />

or STOP condition. State<br />

00H can also occur<br />

when interference<br />

causes SIO1 to enter an<br />

undefined state.<br />

S<br />

08H<br />

1996 Aug 06 28<br />

No S1DAT action No S1CON action Wait or proceed current transfer<br />

No S1DAT action 0 1 0 X Only the internal hardware is affected in the<br />

MST or addressed SLV modes. In all cases,<br />

the bus is released and SIO1 is switched to the<br />

not addressed SLV mode. STO is reset.<br />

SLA W A Data A S Other MST Continues P S SLA<br />

18H 28H 08H<br />

Other Master Sends Repeated<br />

START Condition Earlier<br />

Retry<br />

Figure 21. Simultaneous Repeated START Conditions from 2 Masters