NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Philips Semiconductors<br />

80C51 <strong>Family</strong> Derivatives 8XC552/562 overview<br />

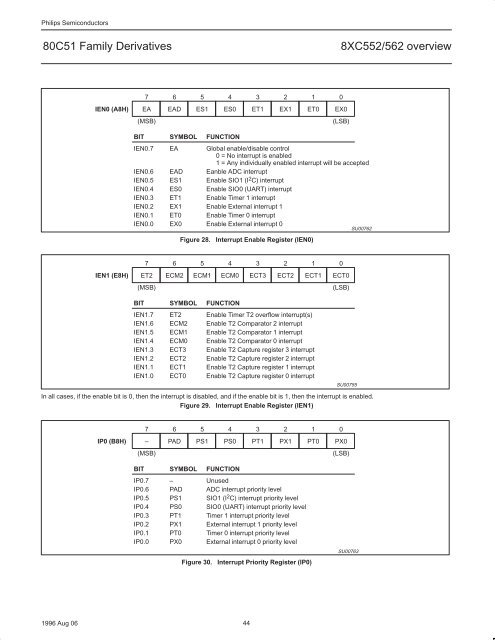

IEN0 (A8H)<br />

IEN1 (E8H)<br />

7<br />

EA<br />

(MSB)<br />

EAD<br />

ES1<br />

ES0<br />

1996 Aug 06 44<br />

6<br />

5<br />

4<br />

ET1<br />

EX1<br />

EX0<br />

BIT SYMBOL FUNCTION<br />

IEN0.7 EA Global enable/disable control<br />

0 = No interrupt is enabled<br />

1 = Any individually enabled interrupt will be accepted<br />

IEN0.6 EAD Eanble ADC interrupt<br />

IEN0.5 ES1 Enable SIO1 (I2C) interrupt<br />

IEN0.4 ES0 Enable SIO0 (UART) interrupt<br />

IEN0.3 ET1 Enable Timer 1 interrupt<br />

IEN0.2 EX1 Enable External interrupt 1<br />

IEN0.1 ET0 Enable Timer 0 interrupt<br />

IEN0.0 EX0 Enable External interrupt 0<br />

SU00762<br />

7<br />

ET2<br />

(MSB)<br />

6<br />

ECM2<br />

Figure 28. Interrupt Enable Register (IEN0)<br />

5<br />

ECM1<br />

ECM0<br />

3<br />

ECT3<br />

2<br />

ECT2<br />

1<br />

ET0<br />

ECT1<br />

BIT SYMBOL FUNCTION<br />

IEN1.7 ET2 Enable Timer T2 overflow interrupt(s)<br />

IEN1.6 ECM2 Enable T2 Comparator 2 interrupt<br />

IEN1.5 ECM1 Enable T2 Comparator 1 interrupt<br />

IEN1.4 ECM0 Enable T2 Comparator 0 interrupt<br />

IEN1.3 ECT3 Enable T2 Capture register 3 interrupt<br />

IEN1.2 ECT2 Enable T2 Capture register 2 interrupt<br />

IEN1.1 ECT1 Enable T2 Capture register 1 interrupt<br />

IEN1.0 ECT0 Enable T2 Capture register 0 interrupt<br />

4<br />

3<br />

2<br />

1<br />

0<br />

(LSB)<br />

0<br />

ECT0<br />

(LSB)<br />

SU00755<br />

In all cases, if the enable bit is 0, then the interrupt is disabled, and if the enable bit is 1, then the interrupt is enabled.<br />

Figure 29. Interrupt Enable Register (IEN1)<br />

IP0 (B8H)<br />

7<br />

–<br />

(MSB)<br />

6<br />

PAD<br />

5<br />

PS1<br />

PS0<br />

PT1<br />

PX1<br />

BIT SYMBOL FUNCTION<br />

IP0.7 – Unused<br />

IP0.6 PAD ADC interrupt priority level<br />

IP0.5 PS1 SIO1 (I2C) interrupt priority level<br />

IP0.4 PS0 SIO0 (UART) interrupt priority level<br />

IP0.3 PT1 Timer 1 interrupt priority level<br />

IP0.2 PX1 External interrupt 1 priority level<br />

IP0.1 PT0 Timer 0 interrupt priority level<br />

IP0.0 PX0 External interrupt 0 priority level<br />

4<br />

Figure 30. Interrupt Priority Register (IP0)<br />

3<br />

2<br />

1<br />

PT0<br />

0<br />

PX0<br />

(LSB)<br />

SU00763