NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

NXP 80C552, 83/87C552, P80C562, P83C562 Family Overview - Keil

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Philips Semiconductors<br />

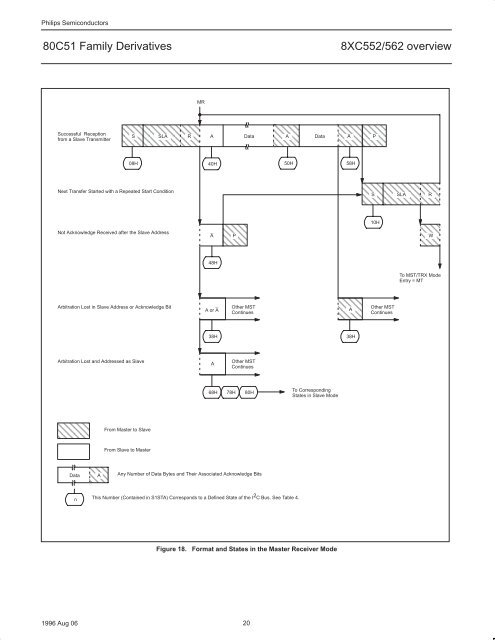

80C51 <strong>Family</strong> Derivatives 8XC552/562 overview<br />

Successful Reception<br />

from a Slave Transmitter<br />

S SLA R A Data A<br />

Data A P<br />

ÇÇÇÇÇÇÇÇ<br />

ÇÇÇÇÇÇÇÇ<br />

Next Transfer Started with a Repeated Start Condition<br />

Not Acknowledge Received after the Slave Address<br />

Arbitration Lost in Slave Address or Acknowledge Bit<br />

Arbitration Lost and Addressed as Slave<br />

ÇÇÇÇ<br />

ÇÇÇÇ<br />

Data A<br />

ÇÇÇÇ<br />

ÇÇ ÇÇÇÇ<br />

n<br />

From Master to Slave<br />

From Slave to Master<br />

08H 40H 50H<br />

A P<br />

ÇÇÇ<br />

ÇÇÇ<br />

A or A<br />

1996 Aug 06 20<br />

MR<br />

48H<br />

38H<br />

A<br />

Other MST<br />

Continues<br />

Other MST<br />

Continues<br />

68H 78H 80H<br />

Any Number of Data Bytes and Their Associated Acknowledge Bits<br />

This Number (Contained in S1STA) Corresponds to a Defined State of the I 2 C Bus. See Table 4.<br />

ÇÇ<br />

ÇÇÇ<br />

ÇÇÇÇ ÇÇÇ<br />

ÇÇÇ<br />

ÇÇÇÇ<br />

ÇÇÇ ÇÇÇ ÇÇÇ<br />

To Corresponding<br />

States in Slave Mode<br />

Figure 18. Format and States in the Master Receiver Mode<br />

58H<br />

ÇÇÇ<br />

A<br />

ÇÇÇ<br />

ÇÇÇ<br />

38H<br />

ÇÇÇÇÇÇÇ<br />

S SLA R<br />

ÇÇÇÇÇÇÇ<br />

ÇÇÇÇÇÇÇ<br />

10H<br />

Other MST<br />

Continues<br />

W<br />

ÇÇÇ<br />

ÇÇÇ<br />

To MST/TRX Mode<br />

Entry = MT