ELEN Elektroniikka- ja sähköalan ennakointi Sähkö- ja ... - Mol.fi

ELEN Elektroniikka- ja sähköalan ennakointi Sähkö- ja ... - Mol.fi

ELEN Elektroniikka- ja sähköalan ennakointi Sähkö- ja ... - Mol.fi

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

úû þ ü ü ÷ þùúùú <br />

FR4 tai vastaava, piirit suo<strong>ja</strong>taan aina alustäytteellä, joka pienentää jännityshuippu<strong>ja</strong> sekä suo<strong>ja</strong>a kosteudelta<br />

<strong>ja</strong> kontaminaatioilta. Suo<strong>ja</strong>us lisää prosessivaiheita <strong>ja</strong> kustannuksia. Alustäyte levitetään erillisellä laitteella <strong>ja</strong><br />

kovetetaan uunissa. Piirit on testattava <strong>ja</strong> kor<strong>ja</strong>ttava ennen suo<strong>ja</strong>usta, koska alustäytteen kovetuttua niitä ei<br />

voi enää poistaa piirilevyltä. Flip Chip -kokoonpanoissa on käytettävä korkealaatuisia piirilevyjä.<br />

þ þ þ øúýüýþ øø÷<br />

<br />

<br />

10 3 100<br />

þùú ýþ<br />

1<br />

ýüù þþùù "tiheä"<br />

ÿþ ý þþýú÷<br />

10 -1 ý ü ù þ þù ù<br />

BGA<br />

10 -3 "erikoistiheä"<br />

10 -2<br />

CSP þ û þ<br />

10 -4<br />

ÿ ÷ý þ ú<br />

ø<br />

10 -5<br />

ø<br />

þ<br />

10 -6<br />

þ þ ý þ þ<br />

ý ü ù ú ú þ ý<br />

ü<br />

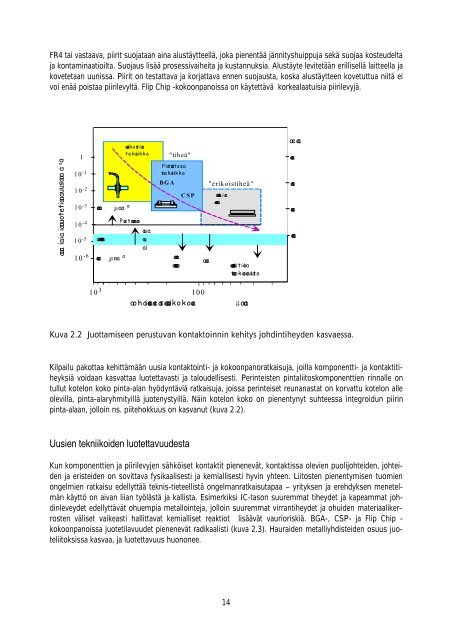

Kuva 2.2 Juottamiseen perustuvan kontaktoinnin kehitys johdintiheyden kasvaessa.<br />

Kilpailu pakottaa kehittämään uusia kontaktointi- <strong>ja</strong> kokoonpanoratkaisu<strong>ja</strong>, joilla komponentti- <strong>ja</strong> kontaktitiheyksiä<br />

voidaan kasvattaa luotettavasti <strong>ja</strong> taloudellisesti. Perinteisten pintaliitoskomponenttien rinnalle on<br />

tullut kotelon koko pinta-alan hyödyntäviä ratkaisu<strong>ja</strong>, joissa perinteiset reunanastat on korvattu kotelon alle<br />

olevilla, pinta-alaryhmityillä juotenystyillä. Näin kotelon koko on pienentynyt suhteessa integroidun piirin<br />

pinta-alaan, jolloin ns. piitehokkuus on kasvanut (kuva 2.2).<br />

Uusien tekniikoiden luotettavuudesta<br />

Kun komponenttien <strong>ja</strong> piirilevyjen sähköiset kontaktit pienenevät, kontaktissa olevien puolijohteiden, johteiden<br />

<strong>ja</strong> eristeiden on sovittava fysikaalisesti <strong>ja</strong> kemiallisesti hyvin yhteen. Liitosten pienentymisen tuomien<br />

ongelmien ratkaisu edellyttää teknis-tieteellistä ongelmanratkaisutapaa – yrityksen <strong>ja</strong> erehdyksen menetelmän<br />

käyttö on aivan liian työlästä <strong>ja</strong> kallista. Esimerkiksi IC-tason suuremmat tiheydet <strong>ja</strong> kapeammat johdinleveydet<br />

edellyttävät ohuempia metallointe<strong>ja</strong>, jolloin suuremmat virrantiheydet <strong>ja</strong> ohuiden materiaalikerrosten<br />

väliset vaikeasti hallittavat kemialliset reaktiot lisäävät vaurioriskiä. BGA-, CSP- <strong>ja</strong> Flip Chip -<br />

kokoonpanoissa juotetilavuudet pienenevät radikaalisti (kuva 2.3). Hauraiden metalliyhdisteiden osuus juoteliitoksissa<br />

kasvaa, <strong>ja</strong> luotettavuus huononee.<br />

14