- Page 2 and 3:

TEKNIK MIKROPROSESOR Penulis : DJOK

- Page 4 and 5:

TEKNIK MIKROPROSESOR KATA PENGANTAR

- Page 6 and 7:

TEKNIK MIKROPROSESOR 3.18. Pengalam

- Page 8 and 9:

TEKNIK MIKROPROSESOR BAB I. PERKEMB

- Page 10 and 11:

TEKNIK MIKROPROSESOR Gambar 1.1. Bl

- Page 12 and 13:

TEKNIK MIKROPROSESOR Prosesor perta

- Page 14 and 15:

TEKNIK MIKROPROSESOR 9 unit ENIAC l

- Page 16 and 17:

TEKNIK MIKROPROSESOR Pada tahun 197

- Page 18 and 19:

TEKNIK MIKROPROSESOR sehingga bagi

- Page 20 and 21:

TEKNIK MIKROPROSESOR Gambar 1.9. Ar

- Page 22 and 23:

TEKNIK MIKROPROSESOR sehingga perke

- Page 24 and 25:

TEKNIK MIKROPROSESOR Mikroprosesor

- Page 26 and 27:

TEKNIK MIKROPROSESOR 5. Era Generas

- Page 28 and 29:

TEKNIK MIKROPROSESOR Peningkatan ke

- Page 30 and 31:

TEKNIK MIKROPROSESOR Gambar 1.11. S

- Page 32 and 33:

TEKNIK MIKROPROSESOR Gambar 1.14. I

- Page 34 and 35:

TEKNIK MIKROPROSESOR 2. Komparasi 8

- Page 36 and 37:

TEKNIK MIKROPROSESOR 12 Beroperasi

- Page 38 and 39:

TEKNIK MIKROPROSESOR 5. Untuk mater

- Page 40 and 41:

TEKNIK MIKROPROSESOR 5. Untuk mater

- Page 42 and 43:

TEKNIK MIKROPROSESOR KOMPETENSI INT

- Page 44 and 45:

TEKNIK MIKROPROSESOR Sedangkan untu

- Page 46 and 47:

TEKNIK MIKROPROSESOR tegangan +/- 1

- Page 48 and 49:

TEKNIK MIKROPROSESOR c. Catu Daya 2

- Page 50 and 51:

TEKNIK MIKROPROSESOR b. Saklar Elek

- Page 52 and 53:

TEKNIK MIKROPROSESOR keluaran push

- Page 54 and 55:

TEKNIK MIKROPROSESOR Gerbang OR min

- Page 56 and 57:

TEKNIK MIKROPROSESOR Tabel kebenara

- Page 58 and 59:

TEKNIK MIKROPROSESOR Gambar 2.8. Ra

- Page 60 and 61:

TEKNIK MIKROPROSESOR Dekoder banyak

- Page 62 and 63:

TEKNIK MIKROPROSESOR Gambar 2.11. A

- Page 64 and 65:

TEKNIK MIKROPROSESOR yang berarti Q

- Page 66 and 67:

TEKNIK MIKROPROSESOR Gambar 2.14. K

- Page 68 and 69:

TEKNIK MIKROPROSESOR Melalui sistem

- Page 70 and 71:

TEKNIK MIKROPROSESOR tn tn+1 K J Q

- Page 72 and 73:

TEKNIK MIKROPROSESOR memori atau po

- Page 74 and 75:

TEKNIK MIKROPROSESOR Gambar 2.22. R

- Page 76 and 77:

TEKNIK MIKROPROSESOR mungkin melaku

- Page 78 and 79:

TEKNIK MIKROPROSESOR b. Setelah clo

- Page 80 and 81:

TEKNIK MIKROPROSESOR Gambar 2.25. P

- Page 82 and 83:

TEKNIK MIKROPROSESOR Gambar 2.29. R

- Page 84 and 85:

TEKNIK MIKROPROSESOR Untuk register

- Page 86 and 87: TEKNIK MIKROPROSESOR e. Penghitung

- Page 88 and 89: TEKNIK MIKROPROSESOR sehingga data

- Page 90 and 91: TEKNIK MIKROPROSESOR yang diperguna

- Page 92 and 93: TEKNIK MIKROPROSESOR 1 0 1 0 1 1 0

- Page 94 and 95: TEKNIK MIKROPROSESOR 0 artinya pada

- Page 96 and 97: TEKNIK MIKROPROSESOR Gambar 2.42. R

- Page 98 and 99: TEKNIK MIKROPROSESOR Br = . A diman

- Page 100 and 101: TEKNIK MIKROPROSESOR fungsi A + B.

- Page 102 and 103: TEKNIK MIKROPROSESOR Jika S2 = 0 ma

- Page 104 and 105: TEKNIK MIKROPROSESOR mengembangkan

- Page 106 and 107: TEKNIK MIKROPROSESOR Dengan jumlah

- Page 108 and 109: TEKNIK MIKROPROSESOR satu clock. De

- Page 110 and 111: TEKNIK MIKROPROSESOR untuk pemroses

- Page 112 and 113: TEKNIK MIKROPROSESOR Keterangan : a

- Page 114 and 115: TEKNIK MIKROPROSESOR Gambar 2.50. K

- Page 116 and 117: TEKNIK MIKROPROSESOR 2.2.8. Kompute

- Page 118 and 119: TEKNIK MIKROPROSESOR Gambar 3.1. Bl

- Page 120 and 121: TEKNIK MIKROPROSESOR Gambar 3.2. Ar

- Page 122 and 123: TEKNIK MIKROPROSESOR alamat adalah

- Page 124 and 125: TEKNIK MIKROPROSESOR Gambar 3.5. Pr

- Page 126 and 127: TEKNIK MIKROPROSESOR c. Relative ad

- Page 128 and 129: TEKNIK MIKROPROSESOR mode 0, yai

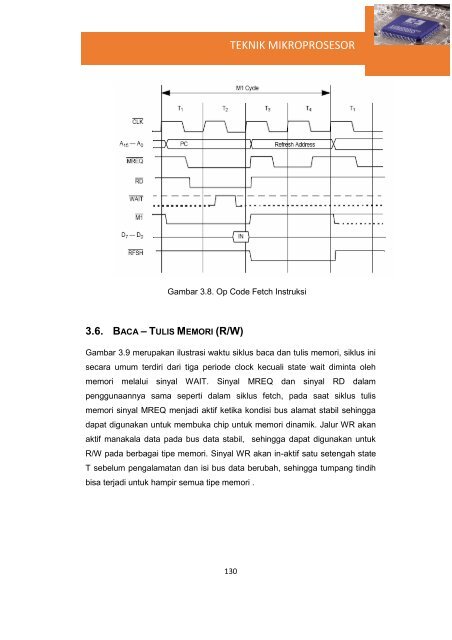

- Page 130 and 131: TEKNIK MIKROPROSESOR dijalankan. Bi

- Page 132 and 133: TEKNIK MIKROPROSESOR Simbol No. PIN

- Page 134 and 135: TEKNIK MIKROPROSESOR Simbol No. PIN

- Page 138 and 139: TEKNIK MIKROPROSESOR Gambar 3.9. Si

- Page 140 and 141: TEKNIK MIKROPROSESOR Jika pemakaian

- Page 142 and 143: TEKNIK MIKROPROSESOR dan lompat ke

- Page 144 and 145: TEKNIK MIKROPROSESOR Gambar 3.15. S

- Page 146: TEKNIK MIKROPROSESOR maskable tidak

- Page 149 and 150: TEKNIK MIKROPROSESOR Pada saat inte

- Page 151 and 152: TEKNIK MIKROPROSESOR Gambar 3.22. R

- Page 153 and 154: TEKNIK MIKROPROSESOR layanan refres

- Page 155 and 156: TEKNIK MIKROPROSESOR Gambar 3.26. P

- Page 157 and 158: TEKNIK MIKROPROSESOR Keterangan pin

- Page 159 and 160: TEKNIK MIKROPROSESOR 2532 4096 x 8

- Page 161 and 162: TEKNIK MIKROPROSESOR 1. Tentukan da

- Page 163 and 164: TEKNIK MIKROPROSESOR pada langkah 1

- Page 165 and 166: TEKNIK MIKROPROSESOR Gambar 3.32 Ra

- Page 167 and 168: TEKNIK MIKROPROSESOR Gambar 3.34 me

- Page 169 and 170: TEKNIK MIKROPROSESOR Kapasitas : 51

- Page 171 and 172: TEKNIK MIKROPROSESOR Sakelar dan LE

- Page 173 and 174: TEKNIK MIKROPROSESOR Gambar 3.37. R

- Page 175 and 176: TEKNIK MIKROPROSESOR A7-A2 dan . me

- Page 177 and 178: TEKNIK MIKROPROSESOR Gambar 3.38. B

- Page 179 and 180: TEKNIK MIKROPROSESOR PPI, walaupun

- Page 181 and 182: TEKNIK MIKROPROSESOR Gambar 3.40. R

- Page 183 and 184: TEKNIK MIKROPROSESOR 5. Aplikasi Fu

- Page 185 and 186: TEKNIK MIKROPROSESOR Fungsi kendali

- Page 187 and 188:

TEKNIK MIKROPROSESOR c. Proses Oper

- Page 189 and 190:

TEKNIK MIKROPROSESOR Gambar 3.43. D

- Page 191 and 192:

TEKNIK MIKROPROSESOR MODE 0 (BASIC

- Page 193 and 194:

TEKNIK MIKROPROSESOR Dengan pengisi

- Page 195 and 196:

TEKNIK MIKROPROSESOR Dengan pengisi

- Page 197 and 198:

TEKNIK MIKROPROSESOR Dengan pengisi

- Page 199 and 200:

TEKNIK MIKROPROSESOR Jawaban 1. Ada

- Page 201 and 202:

TEKNIK MIKROPROSESOR pada paragraf

- Page 203 and 204:

TEKNIK MIKROPROSESOR Gambar 3.48. R

- Page 205 and 206:

TEKNIK MIKROPROSESOR CPU akan menga

- Page 207 and 208:

TEKNIK MIKROPROSESOR Gambar 3.52. R

- Page 209 and 210:

TEKNIK MIKROPROSESOR Gambar 3.54. R

- Page 211 and 212:

TEKNIK MIKROPROSESOR 0 0 0 0 Volt 0

- Page 213 and 214:

TEKNIK MIKROPROSESOR Rangkaian peng

- Page 215 and 216:

TEKNIK MIKROPROSESOR Hasil perhitun

- Page 217 and 218:

TEKNIK MIKROPROSESOR 0. 0 0 0 Volt

- Page 219 and 220:

TEKNIK MIKROPROSESOR 1 1 1 8,75 Vol

- Page 221 and 222:

TEKNIK MIKROPROSESOR 2. Prinsip Ran

- Page 223 and 224:

TEKNIK MIKROPROSESOR Latihan 1. Seb