Teknik Mikroprosesor(1)

Sarana Pendidikan Teknologi Aceh 2016-2020

Sarana Pendidikan Teknologi Aceh 2016-2020

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

TEKNIK MIKROPROSESOR<br />

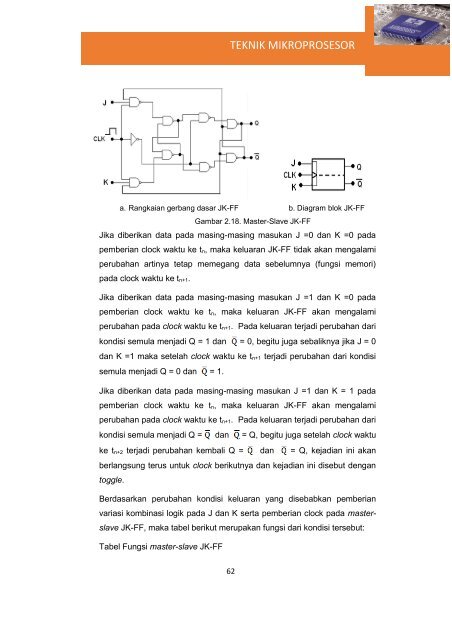

a. Rangkaian gerbang dasar JK-FF b. Diagram blok JK-FF<br />

Gambar 2.18. Master-Slave JK-FF<br />

Jika diberikan data pada masing-masing masukan J =0 dan K =0 pada<br />

pemberian clock waktu ke t n, maka keluaran JK-FF tidak akan mengalami<br />

perubahan artinya tetap memegang data sebelumnya (fungsi memori)<br />

pada clock waktu ke t n+1.<br />

Jika diberikan data pada masing-masing masukan J =1 dan K =0 pada<br />

pemberian clock waktu ke t n, maka keluaran JK-FF akan mengalami<br />

perubahan pada clock waktu ke t n+1. Pada keluaran terjadi perubahan dari<br />

kondisi semula menjadi Q = 1 dan = 0, begitu juga sebaliknya jika J = 0<br />

dan K =1 maka setelah clock waktu ke t n+1 terjadi perubahan dari kondisi<br />

semula menjadi Q = 0 dan = 1.<br />

Jika diberikan data pada masing-masing masukan J =1 dan K = 1 pada<br />

pemberian clock waktu ke t n, maka keluaran JK-FF akan mengalami<br />

perubahan pada clock waktu ke t n+1. Pada keluaran terjadi perubahan dari<br />

kondisi semula menjadi Q = dan = Q, begitu juga setelah clock waktu<br />

ke t n+2 terjadi perubahan kembali Q = dan = Q, kejadian ini akan<br />

berlangsung terus untuk clock berikutnya dan kejadian ini disebut dengan<br />

toggle.<br />

Berdasarkan perubahan kondisi keluaran yang disebabkan pemberian<br />

variasi kombinasi logik pada J dan K serta pemberian clock pada masterslave<br />

JK-FF, maka tabel berikut merupakan fungsi dari kondisi tersebut:<br />

Tabel Fungsi master-slave JK-FF<br />

62