Teknik Mikroprosesor(1)

Sarana Pendidikan Teknologi Aceh 2016-2020

Sarana Pendidikan Teknologi Aceh 2016-2020

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

TEKNIK MIKROPROSESOR<br />

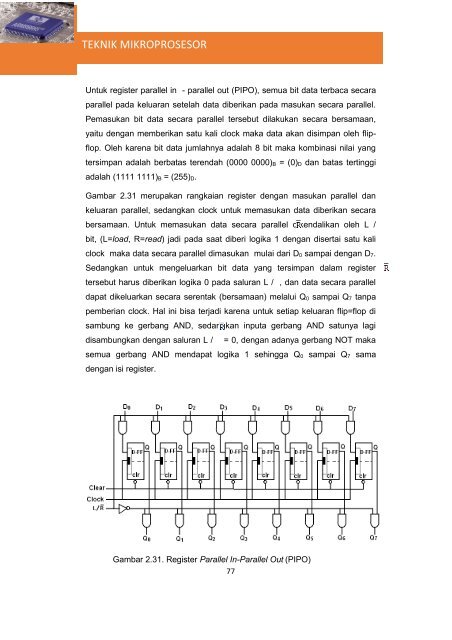

Untuk register parallel in - parallel out (PIPO), semua bit data terbaca secara<br />

parallel pada keluaran setelah data diberikan pada masukan secara parallel.<br />

Pemasukan bit data secara parallel tersebut dilakukan secara bersamaan,<br />

yaitu dengan memberikan satu kali clock maka data akan disimpan oleh flipflop.<br />

Oleh karena bit data jumlahnya adalah 8 bit maka kombinasi nilai yang<br />

tersimpan adalah berbatas terendah (0000 0000) B = (0) D dan batas tertinggi<br />

adalah (1111 1111) B = (255) D.<br />

Gambar 2.31 merupakan rangkaian register dengan masukan parallel dan<br />

keluaran parallel, sedangkan clock untuk memasukan data diberikan secara<br />

bersamaan. Untuk memasukan data secara parallel dikendalikan oleh L /<br />

bit, (L=load, R=read) jadi pada saat diberi logika 1 dengan disertai satu kali<br />

clock maka data secara parallel dimasukan mulai dari D 0 sampai dengan D 7.<br />

Sedangkan untuk mengeluarkan bit data yang tersimpan dalam register<br />

tersebut harus diberikan logika 0 pada saluran L / , dan data secara parallel<br />

dapat dikeluarkan secara serentak (bersamaan) melalui Q 0 sampai Q 7 tanpa<br />

pemberian clock. Hal ini bisa terjadi karena untuk setiap keluaran flip=flop di<br />

sambung ke gerbang AND, sedangkan inputa gerbang AND satunya lagi<br />

disambungkan dengan saluran L / = 0, dengan adanya gerbang NOT maka<br />

semua gerbang AND mendapat logika 1 sehingga Q 0 sampai Q 7 sama<br />

dengan isi register.<br />

Gambar 2.31. Register Parallel In-Parallel Out (PIPO)<br />

77