Informatik 2 - Hochschule Regensburg

Informatik 2 - Hochschule Regensburg

Informatik 2 - Hochschule Regensburg

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

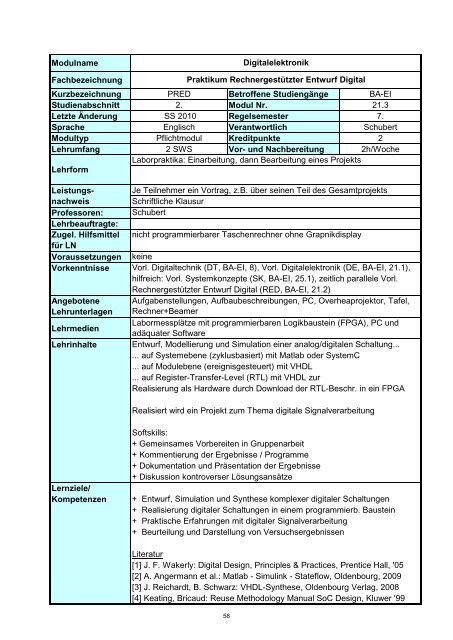

Modulname<br />

Fachbezeichnung<br />

Praktikum Rechnergestützter Entwurf Digital<br />

Kurzbezeichnung PRED Betroffene Studiengänge BA-EI<br />

Studienabschnitt 2. Modul Nr. 21.3<br />

Letzte Änderung SS 2010 Regelsemester 7.<br />

Sprache Englisch Verantwortlich Schubert<br />

Modultyp Pflichtmodul Kreditpunkte 2<br />

Lehrumfang 2 SWS Vor- und Nachbereitung 2h/Woche<br />

Laborpraktika: Einarbeitung, dann Bearbeitung eines Projekts<br />

Lehrform<br />

Leistungsnachweis<br />

Professoren:<br />

Lehrbeauftragte:<br />

Zugel. Hilfsmittel<br />

für LN<br />

Voraussetzungen<br />

Vorkenntnisse<br />

Angebotene<br />

Lehrunterlagen<br />

Lehrmedien<br />

Lehrinhalte<br />

Lernziele/<br />

Kompetenzen<br />

Digitalelektronik<br />

Je Teilnehmer ein Vortrag, z.B. über seinen Teil des Gesamtprojekts<br />

Schriftliche Klausur<br />

Schubert<br />

nicht programmierbarer Taschenrechner ohne Grapnikdisplay<br />

keine<br />

Vorl. Digitaltechnik (DT, BA-EI, 8), Vorl. Digitalelektronik (DE, BA-EI, 21.1),<br />

hilfreich: Vorl. Systemkonzepte (SK, BA-EI, 25.1), zeitlich parallele Vorl.<br />

Rechnergestützter Entwurf Digital (RED, BA-EI, 21.2)<br />

Aufgabenstellungen, Aufbaubeschreibungen, PC, Overheaprojektor, Tafel,<br />

Rechner+Beamer<br />

Labormessplätze mit programmierbaren Logikbaustein (FPGA), PC und<br />

adäquater Software<br />

Entwurf, Modellierung und Simulation einer analog/digitalen Schaltung...<br />

... auf Systemebene (zyklusbasiert) mit Matlab oder SystemC<br />

... auf Modulebene (ereignisgesteuert) mit VHDL<br />

... auf Register-Transfer-Level (RTL) mit VHDL zur<br />

Realisierung als Hardware durch Download der RTL-Beschr. in ein FPGA<br />

Realisiert wird ein Projekt zum Thema digitale Signalverarbeitung<br />

Softskills:<br />

+ Gemeinsames Vorbereiten in Gruppenarbeit<br />

+ Kommentierung der Ergebnisse / Programme<br />

+ Dokumentation und Präsentation der Ergebnisse<br />

+ Diskussion kontroverser Lösungsansätze<br />

+ Entwurf, Simulation und Synthese komplexer digitaler Schaltungen<br />

+ Realisierung digitaler Schaltungen in einem programmierb. Baustein<br />

+ Praktische Erfahrungen mit digitaler Signalverarbeitung<br />

+ Beurteilung und Darstellung von Versuchsergebnissen<br />

Literatur<br />

[1] J. F. Wakerly: Digital Design, Principles & Practices, Prentice Hall, '05<br />

[2] A. Angermann et al.: Matlab - Simulink - Stateflow, Oldenbourg, 2009<br />

[3] J. Reichardt, B. Schwarz: VHDL-Synthese, Oldenbourg Verlag, 2008<br />

[4] Keating, Bricaud: Reuse Methodology Manual SoC Design, Kluwer '99<br />

58