Backside Circuit Edit on Device Level - New Methodologies - Imec

Backside Circuit Edit on Device Level - New Methodologies - Imec

Backside Circuit Edit on Device Level - New Methodologies - Imec

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

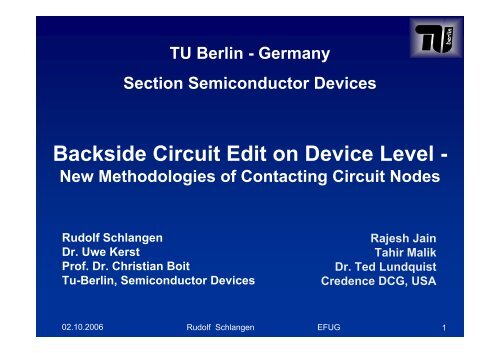

TU Berlin - Germany<br />

Secti<strong>on</strong> Semic<strong>on</strong>ductor <strong>Device</strong>s<br />

<str<strong>on</strong>g>Backside</str<strong>on</strong>g> <str<strong>on</strong>g>Circuit</str<strong>on</strong>g> <str<strong>on</strong>g>Edit</str<strong>on</strong>g> <strong>on</strong> <strong>Device</strong> <strong>Level</strong> -<br />

<strong>New</strong> <strong>Methodologies</strong> of C<strong>on</strong>tacting <str<strong>on</strong>g>Circuit</str<strong>on</strong>g> Nodes<br />

Rudolf Schlangen<br />

Dr. Uwe Kerst<br />

Prof. Dr. Christian Boit<br />

Tu-Berlin, Semic<strong>on</strong>ductor <strong>Device</strong>s<br />

Rajesh Jain<br />

Tahir Malik<br />

Dr. Ted Lundquist<br />

Credence DCG, USA<br />

02.10.2006 Rudolf Schlangen EFUG 1<br />

berlin

Motivati<strong>on</strong><br />

● <strong>New</strong> Packages and high Metal Stacks enforce <str<strong>on</strong>g>Backside</str<strong>on</strong>g> CE<br />

● Shrinking of IC Technology<br />

● Higher <strong>Device</strong> Density<br />

● <str<strong>on</strong>g>Backside</str<strong>on</strong>g> CE becomes more and more difficult<br />

● <strong>New</strong> C<strong>on</strong>tacts offer new Soluti<strong>on</strong>s<br />

02.10.2006 Rudolf Schlangen EFUG 2<br />

berlin

1<br />

2<br />

3<br />

Mechanical thinning to 10 - 40µm<br />

(locally or full die)<br />

FIB - trench to n-well<br />

(100 - 600 µm 2 )<br />

FIB - trench to STI<br />

(4 - 50 µm 2 )<br />

bulk Si<br />

n-well<br />

c<strong>on</strong>trast<br />

7 µm STI<br />

150µm<br />

<str<strong>on</strong>g>Backside</str<strong>on</strong>g> CE Process<br />

NW<br />

W<br />

mechanically removed bulk Silic<strong>on</strong><br />

FIB removed bulk Silic<strong>on</strong><br />

Poly<br />

bulk-Si<br />

02.10.2006 Rudolf Schlangen EFUG 3<br />

STI<br />

IMD<br />

M1<br />

2<br />

3<br />

berlin<br />

1<br />

Si<br />

PW

Output<br />

n-FET<br />

p-FET<br />

120nm Ring Oszillator<br />

Divider<br />

1/1024<br />

RO´s<br />

20µm<br />

bulk Si<br />

STI<br />

actives<br />

150µm<br />

150µm<br />

STI Opening<br />

Trenches<br />

STI Endpoint<br />

N-well<br />

Endpoint<br />

02.10.2006 Rudolf Schlangen EFUG 4<br />

berlin

Output<br />

n-FET<br />

p-FET<br />

120nm Ring Oszillator<br />

Divider<br />

1/1024<br />

RO´s<br />

20µm<br />

bulk Si<br />

STI<br />

actives<br />

02.10.2006 Rudolf Schlangen EFUG 5<br />

STI<br />

M1<br />

X - Secti<strong>on</strong><br />

FIB - SiO 2<br />

350nm<br />

FET<br />

0.4µm<br />

berlin<br />

multiple oversized openings<br />

impact <strong>on</strong> max. frequency > 5%

W<br />

Different Ways to access a <str<strong>on</strong>g>Circuit</str<strong>on</strong>g> Node<br />

1 Targeting M1, M2, M3…<br />

2 C<strong>on</strong>tact to C<strong>on</strong>tact (CtC)<br />

3 C<strong>on</strong>tact to Silicide (CtS)<br />

4 C<strong>on</strong>tact to Poly Si<br />

2 3<br />

1<br />

NW PW<br />

p + n +<br />

p-Poly<br />

CoSi<br />

STI<br />

IMD<br />

M1<br />

FIB deposited Pt<br />

n-Poly<br />

02.10.2006 Rudolf Schlangen EFUG 6<br />

4<br />

berlin

Vdd<br />

● direct c<strong>on</strong>tact to metal<br />

● access to M1, M2, M3, M4<br />

● <strong>on</strong>ly through STI area<br />

C<strong>on</strong>venti<strong>on</strong>al <str<strong>on</strong>g>Backside</str<strong>on</strong>g> CE<br />

access area blocked by:<br />

diffusi<strong>on</strong> area, poly-Si, or lower metal layers<br />

p- MOS<br />

in<br />

Vdd<br />

out<br />

n- MOS<br />

metal 1<br />

metal 2<br />

diffusi<strong>on</strong><br />

02.10.2006 Rudolf Schlangen EFUG 7<br />

GND<br />

berlin<br />

poly - gate<br />

n-well<br />

c<strong>on</strong>tact

● direct c<strong>on</strong>tact to metal<br />

● access to M1, M2, M3, M4<br />

C<strong>on</strong>venti<strong>on</strong>al <str<strong>on</strong>g>Backside</str<strong>on</strong>g> CE<br />

● <strong>on</strong>ly through STI area<br />

access area blocked by:<br />

diffusi<strong>on</strong> area, poly-Si, or lower metal layers<br />

● requires high aspect ratio node access holes<br />

increased via resistance<br />

higher risk for circuitry / CE<br />

02.10.2006 Rudolf Schlangen EFUG 8<br />

berlin

Vdd<br />

● direct c<strong>on</strong>tact to the metal (W)<br />

● reliable Endpoint<br />

● access to “every” signal<br />

● reduced via resistance<br />

p- MOS<br />

similar to every<br />

output in CMOS<br />

C<strong>on</strong>tact to C<strong>on</strong>tact<br />

in<br />

Vdd<br />

out<br />

n- MOS<br />

metal 1<br />

metal 2<br />

diffusi<strong>on</strong><br />

02.10.2006 Rudolf Schlangen EFUG 9<br />

Si<br />

c<strong>on</strong>tacts<br />

0.4µm<br />

GND<br />

STI<br />

berlin<br />

poly - gate<br />

n-well<br />

c<strong>on</strong>tact

● direct c<strong>on</strong>tact to the metal (W)<br />

● reliable Endpoint<br />

● access to “every” signal<br />

● reduced via resistance<br />

● at least 2 c<strong>on</strong>tacts necessary<br />

Pt<br />

STI<br />

350nm<br />

M1<br />

C<strong>on</strong>tact to C<strong>on</strong>tact<br />

sourcedrain<br />

drain source<br />

gate<br />

bulk-Si<br />

node M1 of interest<br />

02.10.2006 Rudolf Schlangen EFUG 10<br />

berlin

Vdd<br />

p- MOS<br />

C<strong>on</strong>tact to Silicide<br />

● c<strong>on</strong>tact to the CoSi Silicide<br />

(CoSi covers every diffusi<strong>on</strong> / active)<br />

● possible without any Metal / C<strong>on</strong>tact<br />

● modificati<strong>on</strong> <strong>on</strong> device level<br />

in<br />

Vdd<br />

out<br />

n- MOS<br />

ONLY<br />

with CtS<br />

metal 1<br />

metal 2<br />

diffusi<strong>on</strong><br />

02.10.2006 Rudolf Schlangen EFUG 11<br />

GND<br />

berlin<br />

poly - gate<br />

n-well<br />

c<strong>on</strong>tact

STI<br />

● cut using lowest Beam Current<br />

Endpoint <strong>on</strong> Silicide<br />

● m<strong>on</strong>itoring the average brightness<br />

IMD<br />

FIB-Pt<br />

n +<br />

CoSi<br />

PW<br />

n-Poly<br />

time [s]<br />

02.10.2006 Rudolf Schlangen EFUG 12<br />

brightness<br />

EPD Tool<br />

CoSi<br />

endpoint<br />

berlin

c<strong>on</strong>tact<br />

last picture of<br />

cut operati<strong>on</strong><br />

Endpoint <strong>on</strong> Silicide<br />

CtS Endpoint Window<br />

02.10.2006 Rudolf Schlangen EFUG 13<br />

berlin

STI p-well<br />

0.5µm<br />

W c<strong>on</strong>tact<br />

M1<br />

FIB created<br />

Pt c<strong>on</strong>tact<br />

IMD source<br />

diff. area<br />

M2<br />

Endpoint <strong>on</strong> Silicide<br />

CoSi<br />

p-well<br />

n-diffusi<strong>on</strong><br />

02.10.2006 Rudolf Schlangen EFUG 14<br />

Pt<br />

berlin

Vdd<br />

● always accessible through STI<br />

● low risk to device<br />

● reliable endpoint<br />

p- MOS<br />

Ct poly Si<br />

C<strong>on</strong>tact to Poly Si<br />

in<br />

Vdd<br />

out<br />

n- MOS<br />

metal 1<br />

metal 2<br />

diffusi<strong>on</strong><br />

02.10.2006 Rudolf Schlangen EFUG 15<br />

GND<br />

berlin<br />

poly - gate<br />

n-well<br />

c<strong>on</strong>tact

poly Si IMD<br />

last picture of<br />

cut operati<strong>on</strong><br />

Endpoint to Poly Si<br />

Poly Si Endpoint Window<br />

02.10.2006 Rudolf Schlangen EFUG 16<br />

berlin

output<br />

1<br />

2<br />

3<br />

4<br />

Inverter Chain<br />

Test <strong>on</strong> Azuma Chip<br />

input<br />

1<br />

2<br />

3<br />

4<br />

CtS<br />

1<br />

n-FET<br />

2<br />

02.10.2006 Rudolf Schlangen EFUG 17<br />

3<br />

4<br />

berlin

output<br />

1<br />

2<br />

3<br />

4<br />

Inverter Chain<br />

Test <strong>on</strong> Azuma Chip<br />

input<br />

1<br />

2<br />

3<br />

4<br />

CtS<br />

n-FET<br />

02.10.2006 Rudolf Schlangen EFUG 18<br />

berlin

output<br />

1<br />

2<br />

3<br />

4<br />

Inverter Chain<br />

CtS n-FET<br />

Ct poly Si<br />

cut<br />

Test <strong>on</strong> Azuma Chip<br />

input<br />

1<br />

2<br />

3<br />

4<br />

02.10.2006 Rudolf Schlangen EFUG 19<br />

berlin<br />

Ct poly Si

output<br />

1<br />

2<br />

3<br />

4<br />

Inverter Chain<br />

CtS n-FET<br />

Ct poly Si<br />

cut<br />

Test <strong>on</strong> Azuma Chip<br />

input<br />

1<br />

2<br />

3<br />

4<br />

02.10.2006 Rudolf Schlangen EFUG 20<br />

berlin

output<br />

1<br />

2<br />

3<br />

4<br />

Inverter Chain<br />

CtS n-FET<br />

Ct poly Si<br />

cut<br />

Test <strong>on</strong> Azuma Chip<br />

input<br />

1<br />

2<br />

3<br />

4<br />

02.10.2006 Rudolf Schlangen EFUG 21<br />

berlin

output<br />

1<br />

2<br />

3<br />

4<br />

Inverter Chain<br />

CtS p-FET<br />

CtS n-FET<br />

Ct poly Si<br />

cut<br />

Test <strong>on</strong> Azuma Chip<br />

input<br />

1<br />

2<br />

3<br />

4<br />

CtS<br />

p-FET<br />

02.10.2006 Rudolf Schlangen EFUG 22<br />

berlin

output<br />

1<br />

2<br />

3<br />

4<br />

Inverter Chain<br />

CtS p-FET<br />

CtS n-FET<br />

Ct poly Si<br />

cut<br />

Test <strong>on</strong> Azuma Chip<br />

input<br />

1<br />

2<br />

3<br />

4<br />

02.10.2006 Rudolf Schlangen EFUG 23<br />

berlin

output<br />

1<br />

2<br />

3<br />

4<br />

Inverter Chain<br />

CtS p-FET<br />

CtS n-FET<br />

Ct poly Si<br />

cut<br />

Test <strong>on</strong> Azuma Chip<br />

input<br />

1<br />

2<br />

3<br />

4<br />

02.10.2006 Rudolf Schlangen EFUG 24<br />

berlin

Summary<br />

● Direct C<strong>on</strong>tact to C<strong>on</strong>tacts, Silicide & Poly presented<br />

● Ct Silicide covers every CMOS Output<br />

● C<strong>on</strong>tact Properties sufficient for Probing and CE<br />

● Via aspect ratio is str<strong>on</strong>gly decreased<br />

● Ct Poly covers every CMOS Input<br />

● Critical high aspect ratio holes <strong>on</strong>ly<br />

needed for cut operati<strong>on</strong>s<br />

02.10.2006 Rudolf Schlangen EFUG 25<br />

Pt<br />

CoSi<br />

berlin<br />

p-well<br />

350 nm<br />

n-diff