BBC Microcomputer Service Manual Oct 1985 Section 1 BBC Micro ...

BBC Microcomputer Service Manual Oct 1985 Section 1 BBC Micro ...

BBC Microcomputer Service Manual Oct 1985 Section 1 BBC Micro ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

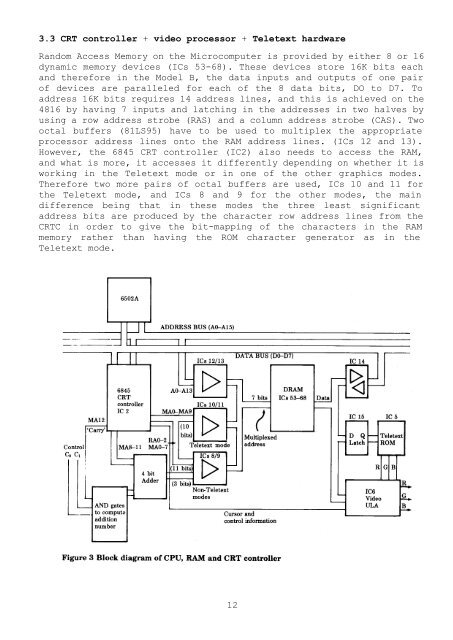

3.3 CRT controller + video processor + Teletext hardware<br />

Random Access Memory on the <strong><strong>Micro</strong>computer</strong> is provided by either 8 or 16<br />

dynamic memory devices (ICs 53-68). These devices store 16K bits each<br />

and therefore in the Model B, the data inputs and outputs of one pair<br />

of devices are paralleled for each of the 8 data bits, DO to D7. To<br />

address 16K bits requires 14 address lines, and this is achieved on the<br />

4816 by having 7 inputs and latching in the addresses in two halves by<br />

using a row address strobe (RAS) and a column address strobe (CAS). Two<br />

octal buffers (81LS95) have to be used to multiplex the appropriate<br />

processor address lines onto the RAM address lines. (ICs 12 and 13).<br />

However, the 6845 CRT controller (IC2) also needs to access the RAM,<br />

and what is more, it accesses it differently depending on whether it is<br />

working in the Teletext mode or in one of the other graphics modes.<br />

Therefore two more pairs of octal buffers are used, ICs 10 and 11 for<br />

the Teletext mode, and ICs 8 and 9 for the other modes, the main<br />

difference being that in these modes the three least significant<br />

address bits are produced by the character row address lines from the<br />

CRTC in order to give the bit-mapping of the characters in the RAM<br />

memory rather than having the ROM character generator as in the<br />

Teletext mode.<br />

12