Intel 45nm Process Overview - UCSB CAD & Test

Intel 45nm Process Overview - UCSB CAD & Test

Intel 45nm Process Overview - UCSB CAD & Test

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

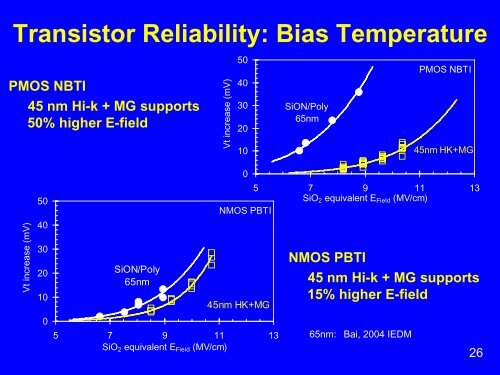

Transistor Reliability: Bias Temperature<br />

PMOS NBTI<br />

Vt increase (mV)<br />

45 nm Hi-k + MG supports<br />

50% higher E-field<br />

50<br />

40<br />

30<br />

20<br />

10<br />

0<br />

SiON/Poly<br />

65nm<br />

Vt increase (mV)<br />

5 7 9 11 13<br />

SiO2 equivalent EField (MV/cm)<br />

50<br />

40<br />

30<br />

20<br />

10<br />

0<br />

SiON/Poly<br />

65nm<br />

PMOS NBTI<br />

<strong>45nm</strong> HK+MG<br />

5 7 9 11 13<br />

SiO2 equivalent EField (MV/cm)<br />

NMOS PBTI<br />

<strong>45nm</strong> HK+MG<br />

NMOS PBTI<br />

45 nm Hi-k + MG supports<br />

15% higher E-field<br />

65nm: Bai, 2004 IEDM<br />

26