Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

广州周立功单片机发展有限公司 Tel (020)38730976 38730916 Fax 38730925 http //www.zlgmcu.com<br />

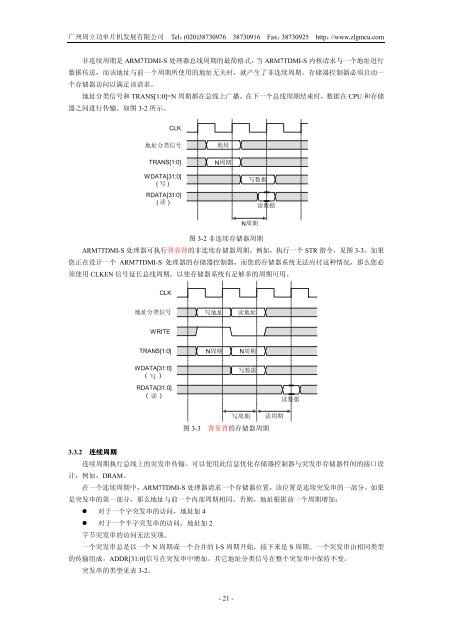

非连续周期是 <strong>ARM7TDMI</strong>-S 处理器总线周期的最简格式 当 <strong>ARM7TDMI</strong>-S 内核请求与一个地址进行<br />

数据传送 而该地址与前一个周期所使用的地址无关时 就产生了非连续周期 存储器控制器必须启动一<br />

个存储器访问以满足该请求<br />

地址分类信号和 TRANS[1:0]=N 周期都在总线上广播 在下一个总线周期结束时 数据在 CPU 和存储<br />

器之间进行传输 如图 3-2 所示<br />

CLK<br />

地址分类信号<br />

TRANS[1:0]<br />

WDATA[31:0]<br />

( 写 )<br />

RDATA[31:0]<br />

( 读 )<br />

地址<br />

N周期<br />

- 21 -<br />

写数据<br />

N周期<br />

读数据<br />

图 3-2 非连续存储器周期<br />

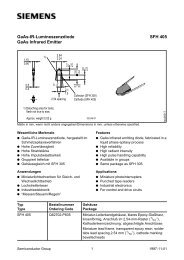

<strong>ARM7TDMI</strong>-S 处理器可执行背靠背的非连续存储器周期 例如 执行一个 STR 指令 见图 3-3 如果<br />

您正在设计一个 <strong>ARM7TDMI</strong>-S 处理器的存储器控制器 而您的存储器系统无法应付这种情况 那么您必<br />

须使用 CLKEN 信号延长总线周期 以使存储器系统有足够多的周期可用<br />

CLK<br />

地址分类信号<br />

WRITE<br />

TRANS[1:0]<br />

WDATA[31:0]<br />

( 写 )<br />

RDATA[31:0]<br />

( 读 )<br />

写地址<br />

N周期<br />

读地址<br />

N周期<br />

写数据<br />

写周期 读周期<br />

图 3-3 背靠背的存储器周期<br />

读数据<br />

3.3.2 连续周期<br />

连续周期<br />

连续周期执行总线上的突发串传输 可以使用此信息优化存储器控制器与突发串存储器件间的接口设<br />

计 例如 DRAM<br />

在一个连续周期中 <strong>ARM7TDMI</strong>-S 处理器请求一个存储器位置 该位置是连续突发串的一部分 如果<br />

是突发串的第一部分 那么地址与前一个内部周期相同 否则 地址根据前一个周期增加<br />

对于一个字突发串的访问 地址加 4<br />

对于一个半字突发串的访问<br />

字节突发串的访问无法实现<br />

地址加 2<br />

一个突发串总是以一个 N 周期或一个合并的 I-S 周期开始 接下来是 S 周期 一个突发串由相同类型<br />

的传输组成 ADDR[31:0]信号在突发串中增加 其它地址分类信号在整个突发串中保持不变<br />

突发串的类型见表 3-2