Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

广州周立功单片机发展有限公司 Tel (020)38730976 38730916 Fax 38730925 http //www.zlgmcu.com<br />

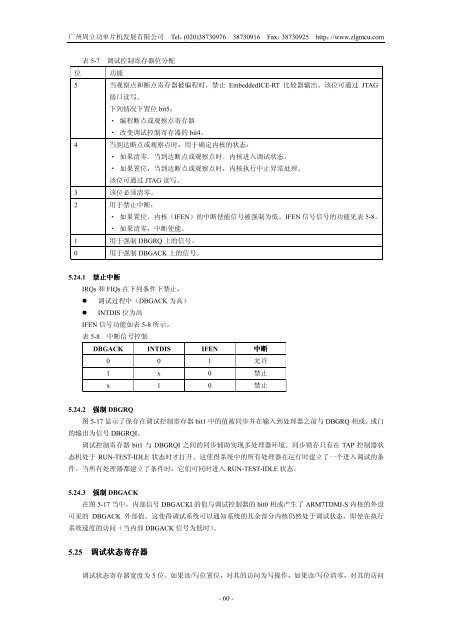

表 5-7 调试控制寄存器位分配<br />

位 功能<br />

5 当观察点和断点寄存器被编程时<br />

接口读写<br />

下列情况下置位 bit5<br />

禁止 EmbeddedICE-RT 比较器输出 该位可通过 JTAG<br />

编程断点或观察点寄存器<br />

改变调试控制寄存器的 bit4<br />

4 当到达断点或观察点时 用于确定内核的状态<br />

如果清零 当到达断点或观察点时 内核进入调试状态<br />

如果置位 当到达断点或观察点时 内核执行中止异常处理<br />

该位可通过 JTAG 读写<br />

3 该位必须清零<br />

2 用于禁止中断<br />

如果置位 内核 IFEN 的中断使能信号被强制为低 IFEN 信号信号的功能见表 5-8<br />

如果清零 中断使能<br />

1 用于强制 DBGRQ 上的信号<br />

0 用于强制 DBGACK 上的信号<br />

5.24.1 禁止中断<br />

禁止中断<br />

IRQs 和 FIQs 在下列条件下禁止<br />

调试过程中 DBGACK 为高<br />

INTDIS 位为高<br />

IFEN 信号功能如表 5-8 所示<br />

表 5-8 中断信号控制<br />

DBGACK INTDIS IFEN 中断<br />

中断<br />

0 0 1 允许<br />

1 x 0 禁止<br />

x 1 0 禁止<br />

5.24.2 强制 强制 DBGRQ<br />

图 5-17 显示了保存在调试控制寄存器 bit1 中的值被同步并在输入到处理器之前与 DBGRQ 相或<br />

的输出为信号 DBGRQI<br />

或门<br />

调试控制寄存器 bit1 与 DBGRQI 之间的同步辅助实现多处理器环境 同步锁存只有在 TAP 控制器状<br />

态机处于 RUN-TEST-IDLE 状态时才打开 这使得系统中的所有处理器在运行时建立了一个进入调试的条<br />

件 当所有处理器都建立了条件时 它们可同时进入 RUN-TEST-IDLE 状态<br />

5.24.3 强制 强制 强制 DBGACK<br />

在图 5-17 当中 内部信号 DBGACKI 的值与调试控制器的 bit0 相或产生了 <strong>ARM7TDMI</strong>-S 内核的外设<br />

可见的 DBGACK 外部值 这使得调试系统可以通知系统的其余部分内核仍然处于调试状态 即使在执行<br />

系统速度的访问 当内部 DBGACK 信号为低时<br />

5.25 调试状态寄存器<br />

调试状态寄存器<br />

调试状态寄存器宽度为 5 位 如果读/写位置位 对其的访问为写操作 如果读/写位清零 对其的访问<br />

- 60 -