You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

广州周立功单片机发展有限公司 Tel (020)38730976 38730916 Fax 38730925 http //www.zlgmcu.com<br />

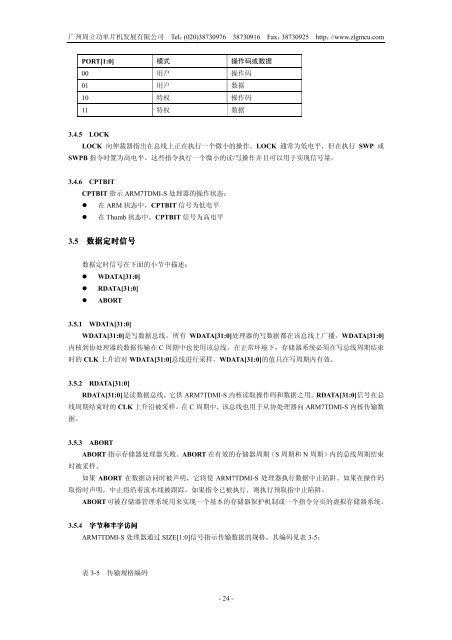

PORT[1:0] 模式 操作码或数据<br />

00 用户 操作码<br />

01 用户 数据<br />

10 特权 操作码<br />

11 特权 数据<br />

3.4.5 LOCK<br />

LOCK 向仲裁器指出在总线上正在执行一个微小的操作 LOCK 通常为低电平 但在执行 SWP 或<br />

SWPB 指令时置为高电平 这些指令执行一个微小的读/写操作并且可以用于实现信号量<br />

3.4.6 CPTBIT<br />

CPTBIT 指示 <strong>ARM7TDMI</strong>-S 处理器的操作状态<br />

在 ARM 状态中 CPTBIT 信号为低电平<br />

在 Thumb 状态中 CPTBIT 信号为高电平<br />

3.5 数据定时信号<br />

数据定时信号<br />

数据定时信号在下面的小节中描述<br />

WDATA[31:0]<br />

RDATA[31:0]<br />

ABORT<br />

3.5.1 WDATA[31:0]<br />

WDATA[31:0]是写数据总线 所有 WDATA[31:0]处理器的写数据都在该总线上广播 WDATA[31:0]<br />

内核到协处理器的数据传输在 C 周期中也使用该总线 在正常环境下 存储器系统必须在写总线周期结束<br />

时的 CLK 上升沿对 WDATA[31:0]总线进行采样 WDATA[31:0]的值只在写周期内有效<br />

3.5.2 RDATA[31:0]<br />

RDATA[31:0]是读数据总线 它供 <strong>ARM7TDMI</strong>-S 内核读取操作码和数据之用 RDATA[31:0]信号在总<br />

线周期结束时的 CLK 上升沿被采样<br />

据<br />

在 C 周期中 该总线也用于从协处理器向 <strong>ARM7TDMI</strong>-S 内核传输数<br />

3.5.3 ABORT<br />

ABORT 指示存储器处理器失败<br />

时被采样<br />

ABORT 在有效的存储器周期 S 周期和 N 周期 内的总线周期结束<br />

如果 ABORT 在数据访问时被声明 它将使 <strong>ARM7TDMI</strong>-S 处理器执行数据中止陷阱 如果在操作码<br />

取指时声明 中止将沿着流水线被跟踪 如果指令已被执行 则执行预取指中止陷阱<br />

ABORT 可被存储器管理系统用来实现一个基本的存储器保护机制或一个指令分页的虚拟存储器系统<br />

3.5.4 字节和半字访问<br />

字节和半字访问<br />

字节和半字访问<br />

<strong>ARM7TDMI</strong>-S 处理器通过 SIZE[1:0]信号指示传输数据的规格 其编码见表 3-5<br />

表 3-5 传输规格编码<br />

- 24 -