Intel 64 and IA-32 Architectures Software Developer's Manual

Intel 64 and IA-32 Architectures Software Developer's Manual

Intel 64 and IA-32 Architectures Software Developer's Manual

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Documentation Changes<br />

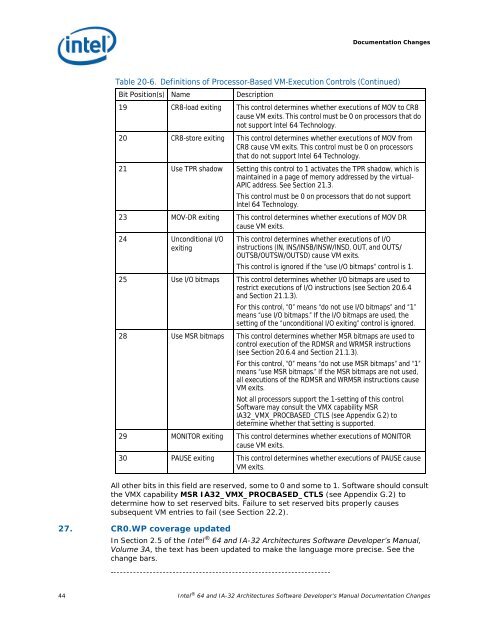

Table 20-6. Definitions of Processor-Based VM-Execution Controls (Continued)<br />

Bit Position(s) Name Description<br />

19 CR8-load exiting This control determines whether executions of MOV to CR8<br />

cause VM exits. This control must be 0 on processors that do<br />

not support <strong>Intel</strong> <strong>64</strong> Technology.<br />

20 CR8-store exiting This control determines whether executions of MOV from<br />

CR8 cause VM exits. This control must be 0 on processors<br />

that do not support <strong>Intel</strong> <strong>64</strong> Technology.<br />

21 Use TPR shadow Setting this control to 1 activates the TPR shadow, which is<br />

maintained in a page of memory addressed by the virtual-<br />

APIC address. See Section 21.3.<br />

This control must be 0 on processors that do not support<br />

<strong>Intel</strong> <strong>64</strong> Technology.<br />

23 MOV-DR exiting This control determines whether executions of MOV DR<br />

cause VM exits.<br />

24 Unconditional I/O<br />

exiting<br />

This control determines whether executions of I/O<br />

instructions (IN, INS/INSB/INSW/INSD, OUT, <strong>and</strong> OUTS/<br />

OUTSB/OUTSW/OUTSD) cause VM exits.<br />

This control is ignored if the “use I/O bitmaps” control is 1.<br />

25 Use I/O bitmaps This control determines whether I/O bitmaps are used to<br />

restrict executions of I/O instructions (see Section 20.6.4<br />

<strong>and</strong> Section 21.1.3).<br />

For this control, “0” means “do not use I/O bitmaps” <strong>and</strong> “1”<br />

means “use I/O bitmaps.” If the I/O bitmaps are used, the<br />

setting of the “unconditional I/O exiting” control is ignored.<br />

28 Use MSR bitmaps This control determines whether MSR bitmaps are used to<br />

control execution of the RDMSR <strong>and</strong> WRMSR instructions<br />

(see Section 20.6.4 <strong>and</strong> Section 21.1.3).<br />

For this control, “0” means “do not use MSR bitmaps” <strong>and</strong> “1”<br />

means “use MSR bitmaps.” If the MSR bitmaps are not used,<br />

all executions of the RDMSR <strong>and</strong> WRMSR instructions cause<br />

VM exits.<br />

Not all processors support the 1-setting of this control.<br />

<strong>Software</strong> may consult the VMX capability MSR<br />

<strong>IA</strong><strong>32</strong>_VMX_PROCBASED_CTLS (see Appendix G.2) to<br />

determine whether that setting is supported.<br />

29 MONITOR exiting This control determines whether executions of MONITOR<br />

cause VM exits.<br />

30 PAUSE exiting This control determines whether executions of PAUSE cause<br />

VM exits.<br />

All other bits in this field are reserved, some to 0 <strong>and</strong> some to 1. <strong>Software</strong> should consult<br />

the VMX capability MSR <strong>IA</strong><strong>32</strong>_VMX_PROCBASED_CTLS (see Appendix G.2) to<br />

determine how to set reserved bits. Failure to set reserved bits properly causes<br />

subsequent VM entries to fail (see Section 22.2).<br />

27. CR0.WP coverage updated<br />

In Section 2.5 of the <strong>Intel</strong> ® <strong>64</strong> <strong>and</strong> <strong>IA</strong>-<strong>32</strong> <strong>Architectures</strong> <strong>Software</strong> Developer’s <strong>Manual</strong>,<br />

Volume 3A, the text has been updated to make the language more precise. See the<br />

change bars.<br />

-------------------------------------------------------------------<br />

44 <strong>Intel</strong> ® <strong>64</strong> <strong>and</strong> <strong>IA</strong>-<strong>32</strong> <strong>Architectures</strong> <strong>Software</strong> Developer’s <strong>Manual</strong> Documentation Changes