Intel 64 and IA-32 Architectures Software Developer's Manual

Intel 64 and IA-32 Architectures Software Developer's Manual

Intel 64 and IA-32 Architectures Software Developer's Manual

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

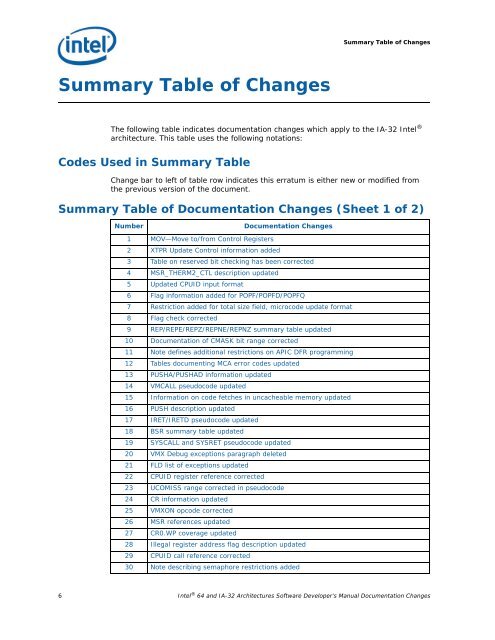

Summary Table of Changes<br />

Summary Table of Changes<br />

The following table indicates documentation changes which apply to the <strong>IA</strong>-<strong>32</strong> <strong>Intel</strong> ®<br />

architecture. This table uses the following notations:<br />

Codes Used in Summary Table<br />

Change bar to left of table row indicates this erratum is either new or modified from<br />

the previous version of the document.<br />

Summary Table of Documentation Changes (Sheet 1 of 2)<br />

Number<br />

Documentation Changes<br />

1 MOV—Move to/from Control Registers<br />

2 XTPR Update Control information added<br />

3 Table on reserved bit checking has been corrected<br />

4 MSR_THERM2_CTL description updated<br />

5 Updated CPUID input format<br />

6 Flag information added for POPF/POPFD/POPFQ<br />

7 Restriction added for total size field, microcode update format<br />

8 Flag check corrected<br />

9 REP/REPE/REPZ/REPNE/REPNZ summary table updated<br />

10 Documentation of CMASK bit range corrected<br />

11 Note defines additional restrictions on APIC DFR programming<br />

12 Tables documenting MCA error codes updated<br />

13 PUSHA/PUSHAD information updated<br />

14 VMCALL pseudocode updated<br />

15 Information on code fetches in uncacheable memory updated<br />

16 PUSH description updated<br />

17 IRET/IRETD pseudocode updated<br />

18 BSR summary table updated<br />

19 SYSCALL <strong>and</strong> SYSRET pseudocode updated<br />

20 VMX Debug exceptions paragraph deleted<br />

21 FLD list of exceptions updated<br />

22 CPUID register reference corrected<br />

23 UCOMISS range corrected in pseudocode<br />

24 CR information updated<br />

25 VMXON opcode corrected<br />

26 MSR references updated<br />

27 CR0.WP coverage updated<br />

28 Illegal register address flag description updated<br />

29 CPUID call reference corrected<br />

30 Note describing semaphore restrictions added<br />

6 <strong>Intel</strong> ® <strong>64</strong> <strong>and</strong> <strong>IA</strong>-<strong>32</strong> <strong>Architectures</strong> <strong>Software</strong> Developer’s <strong>Manual</strong> Documentation Changes