A formal description of SYSTEM/360

A formal description of SYSTEM/360

A formal description of SYSTEM/360

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

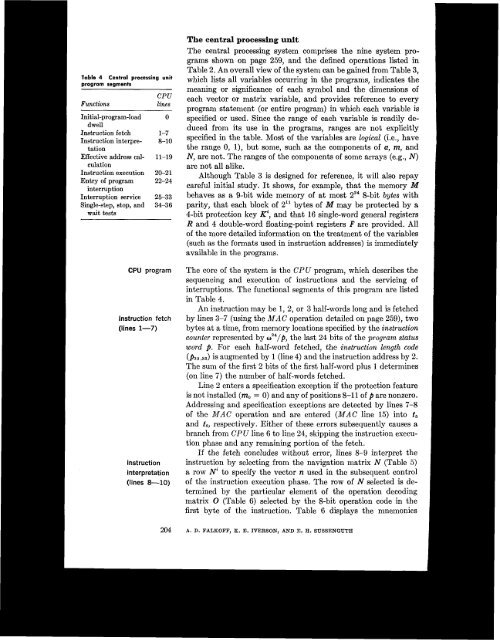

Table 4 Central processing unitprogram segmentsFunctionsCPUlinesInitial-program-load 0dwellInstruction fetch 1-7Instruction interpre- 8-10tationEffective address cal- 11-19culationInstruction execution 20-21Entry <strong>of</strong> program 22-24interruptionInterruption service 25-33Single-step, stop, and 34-36wait testsCPU programinstruction fetch(lines 1-7)instructioninterpretation(lines 8-10)204The central processing unitThe central processing system comprises the nine system programsshown on page 259, and the defined operations listed inTable 2. An overall view <strong>of</strong> the system can be gained from Table 3,which lists all variables occurring in the programs, indicates themeaning or significance <strong>of</strong> each symbol and the dimensions <strong>of</strong>each vector or matrix variable, and provides reference to everyprogram statement (or entire program) in which each variable isspecified or used. Since the range <strong>of</strong> each variable is readily deducedfrom its use in the programs, ranges are not explicitlyspecified in the table. Most <strong>of</strong> the variables are logical (i.e., havethe range 0, l), but some, such as the components <strong>of</strong> a, m, andN, are not. The ranges <strong>of</strong> the components <strong>of</strong> some arrays (e.g., N)are not all alike.Although Table 3 is designed for reference, it will also repaycareful initial study. It shows, for example, that the memory Mbehaves as a 9-bit wide memory <strong>of</strong> at most 224 8-bit bytes withparity, that each block <strong>of</strong> 2" bytes <strong>of</strong> M may be protected by a4-bit protection key K', and that 16 single-word general registersR and 4 double-word floating-point registers F are provided. All<strong>of</strong> the more detailed information on the treatment <strong>of</strong> the variables(such as the formats used in instruction addresses) is immediatelyavailable in the programs.The core <strong>of</strong> the system is the CPU program, which describes thesequencing and execution <strong>of</strong> instructions and the servicing <strong>of</strong>interruptions. The functional segments <strong>of</strong> this program are listedin Table 4.An instruction may be 1, 2, or 3 half-words long and is fetchedby lines 3-7 (using the MAC operation detailed on page 259), twobytes at a time, from memory locations specified by the instructioncounter represented by ""/pa, the last 24 bits <strong>of</strong> the program statusword p. For each half-word fetched, the instruction length code(p32,) is augmented by 1 (line 4) and the instruction address by 2.The sum <strong>of</strong> the first 2 bits <strong>of</strong> the first half-word plus 1 determines(on line 7) the number <strong>of</strong> half-words fetched.Line 2 enters a specification exception if the protection featureis not installed (m, = 0) and any <strong>of</strong> positions 8-11 <strong>of</strong> p are nonzero.Addressing and specification exceptions are detected by lines 7-8<strong>of</strong> the MAC operation and are entered (MAC line 15) into tsand is, respectively. Either <strong>of</strong> these errors subsequently causes abranch from CPU line 6 to line 24, skipping the instruction executionphase and any remaining portion <strong>of</strong> the fetch.If the fetch concludes without error, lines 8-9 interpret theinstruction by selecting from the navigation matrix N (Table 5)a row N" to specify the vector n used in the subsequent control<strong>of</strong> the instruction execution phase. The row<strong>of</strong> N selected is determinedby the particular element <strong>of</strong> the operation decodingmatrix 0 (Table 6) selected by the 8-bit operation code in thefirst byte <strong>of</strong> the instruction. Table 6 displays the mnemonicsA. D. FALKOFF, K. E. IVERSON, AND E. H. SUSSENGUTH