Carbon UART PL011 Model User Guide for SoC Designer

Carbon UART PL011 Model User Guide for SoC Designer

Carbon UART PL011 Model User Guide for SoC Designer

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

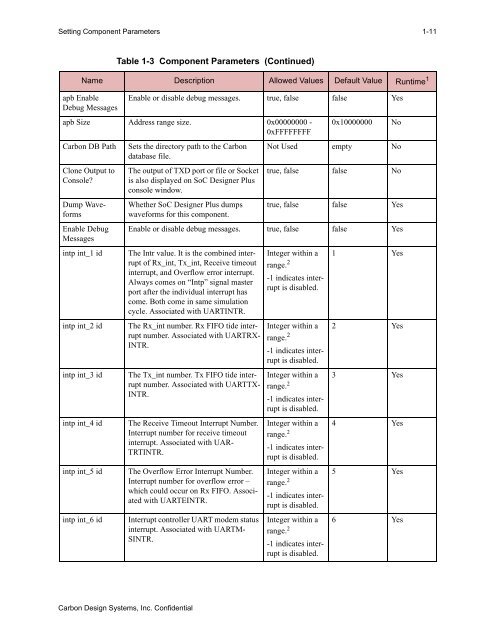

Setting Component Parameters 1-11apb EnableDebug MessagesEnable or disable debug messages. true, false false Yesapb Size Address range size. 0x00000000 -0xFFFFFFFF<strong>Carbon</strong> DB PathClone Output toConsole?Dump Wave<strong>for</strong>msEnable DebugMessagesintp int_1 idintp int_2 idintp int_3 idintp int_4 idintp int_5 idintp int_6 idTable 1-3 Component Parameters (Continued)Name Description Allowed Values Default Value Runtime 1Sets the directory path to the <strong>Carbon</strong>database file.The output of TXD port or file or Socketis also displayed on <strong>SoC</strong> <strong>Designer</strong> Plusconsole window.Whether <strong>SoC</strong> <strong>Designer</strong> Plus dumpswave<strong>for</strong>ms <strong>for</strong> this component.0x10000000NoNot Used empty Notrue, false false Notrue, false false YesEnable or disable debug messages. true, false false YesThe Intr value. It is the combined interruptof Rx_int, Tx_int, Receive timeoutinterrupt, and Overflow error interrupt.Always comes on “Intp” signal masterport after the individual interrupt hascome. Both come in same simulationcycle. Associated with <strong>UART</strong>INTR.The Rx_int number. Rx FIFO tide interruptnumber. Associated with <strong>UART</strong>RX-INTR.The Tx_int number. Tx FIFO tide interruptnumber. Associated with <strong>UART</strong>TX-INTR.The Receive Timeout Interrupt Number.Interrupt number <strong>for</strong> receive timeoutinterrupt. Associated with UAR-TRTINTR.The Overflow Error Interrupt Number.Interrupt number <strong>for</strong> overflow error –which could occur on Rx FIFO. Associatedwith <strong>UART</strong>EINTR.Interrupt controller <strong>UART</strong> modem statusinterrupt. Associated with <strong>UART</strong>M-SINTR.Integer within arange. 2-1 indicates interruptis disabled.Integer within arange. 2-1 indicates interruptis disabled.Integer within arange. 2-1 indicates interruptis disabled.Integer within arange. 2-1 indicates interruptis disabled.Integer within arange. 2-1 indicates interruptis disabled.Integer within arange. 2-1 indicates interruptis disabled.1 Yes2 Yes3 Yes4 Yes5 Yes6 Yes<strong>Carbon</strong> Design Systems, Inc. Confidential