Chapter 4 Introduction

Chapter 4 Introduction

Chapter 4 Introduction

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

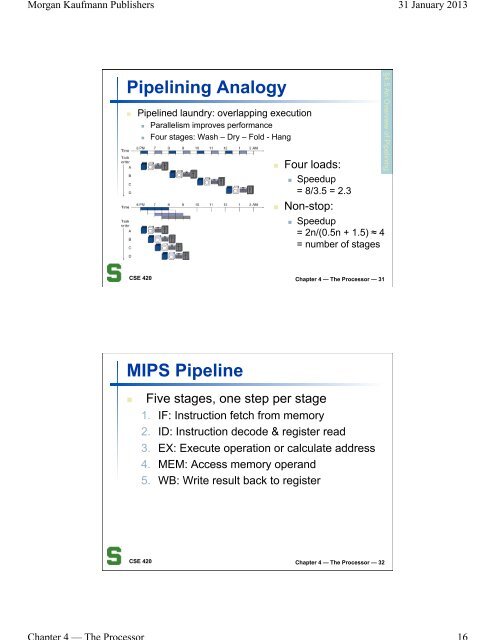

Morgan Kaufmann Publishers 31 January 2013Pipelining AnalogynPipelined laundry: overlapping executionn Parallelism improves performancen Four stages: Wash – Dry – Fold - Hangn Four loads:n Speedup= 8/3.5 = 2.3n Non-stop:nSpeedup= 2n/(0.5n + 1.5) ≈ 4= number of stages§4.5 An Overview of PipeliningCSE 420 <strong>Chapter</strong> 4 — The Processor — 31MIPS PipelinenFive stages, one step per stage1. IF: Instruction fetch from memory2. ID: Instruction decode & register read3. EX: Execute operation or calculate address4. MEM: Access memory operand5. WB: Write result back to registerCSE 420 <strong>Chapter</strong> 4 — The Processor — 32