Chapter 4 Introduction

Chapter 4 Introduction

Chapter 4 Introduction

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

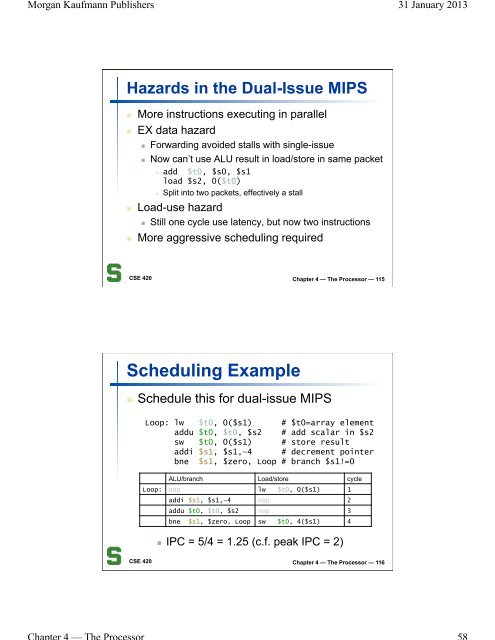

Morgan Kaufmann Publishers 31 January 2013Hazards in the Dual-Issue MIPSn More instructions executing in paralleln EX data hazardn Forwarding avoided stalls with single-issuenNow can’t use ALU result in load/store in same packetn add $t0, $s0, $s1load $s2, 0($t0)n Split into two packets, effectively a stalln Load-use hazardn Still one cycle use latency, but now two instructionsn More aggressive scheduling requiredCSE 420 <strong>Chapter</strong> 4 — The Processor — 115Scheduling Examplen Schedule this for dual-issue MIPSLoop: lw $t0, 0($s1) # $t0=array elementaddu $t0, $t0, $s2 # add scalar in $s2sw $t0, 0($s1) # store resultaddi $s1, $s1,–4 # decrement pointerbne $s1, $zero, Loop # branch $s1!=0ALU/branch Load/store cycleLoop: nop lw $t0, 0($s1) 1addi $s1, $s1,–4 nop 2addu $t0, $t0, $s2 nop 3bne $s1, $zero, Loop sw $t0, 4($s1) 4n IPC = 5/4 = 1.25 (c.f. peak IPC = 2)CSE 420 <strong>Chapter</strong> 4 — The Processor — 116